sim.bat:windows批处理文件,用于启动modelsim,然后运行sim.do文件; {代码...} 注意:modelsim在安装的时候需要加入到环境变量。

译文现场可编程逻辑门阵列(FPGAs)在安全关键系统中的安全性认证(上)关键词:现场可编程逻辑门阵列、可编程序逻辑、安全认证、安全评估...

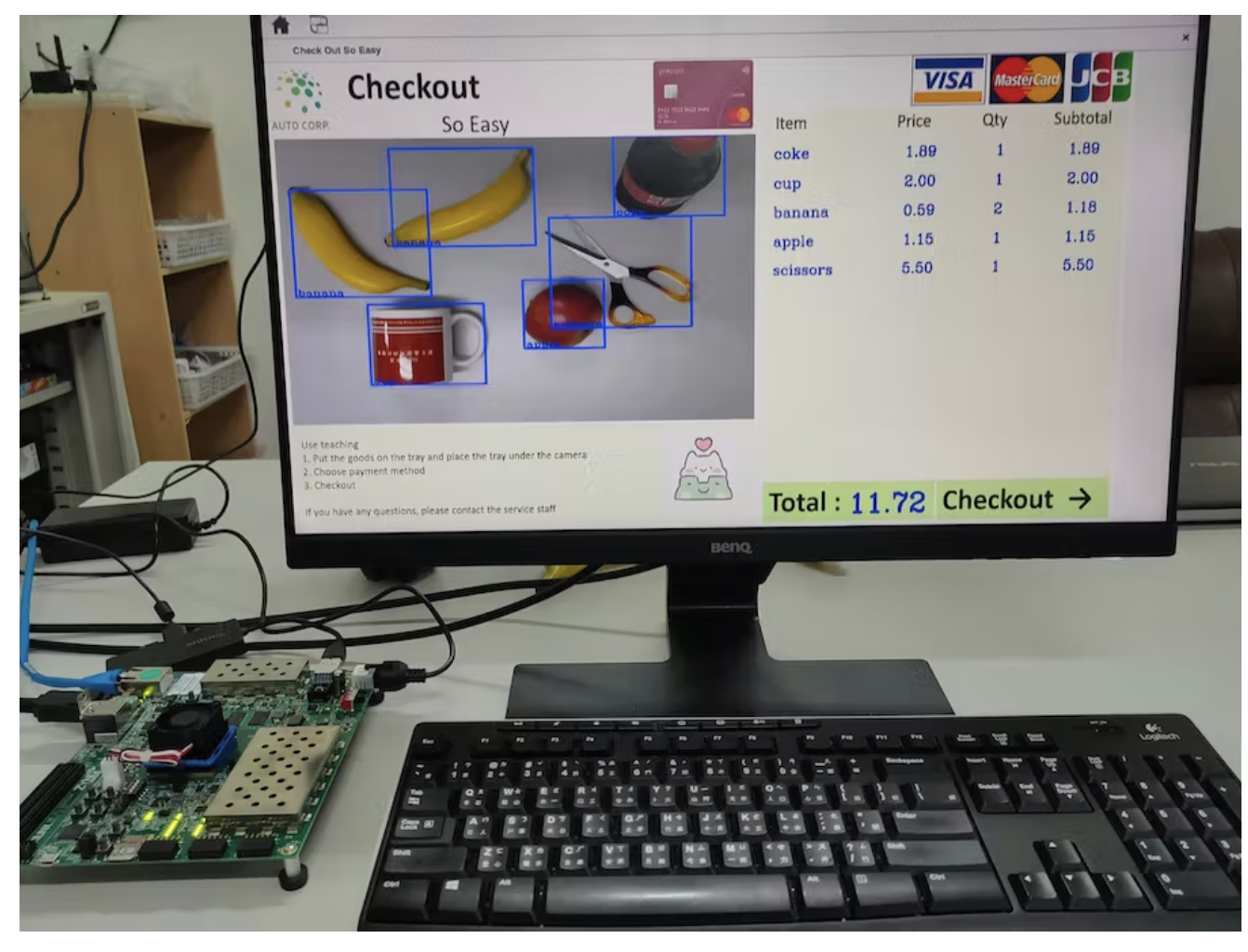

整个系统是以DPU为核心,在 DPU 上部署对象检测模型实现实时智能检测,该系统视频输入可以来自 VCU 解码的视频或来自相机的实时视频图像。

绪论查看《为什么FPGA/ADC通信在工业领域下更喜欢用GPMC接口?》了解TinyML~今天介绍几个与TinyML相关的开源项目。TinyML Cookbook[链接...

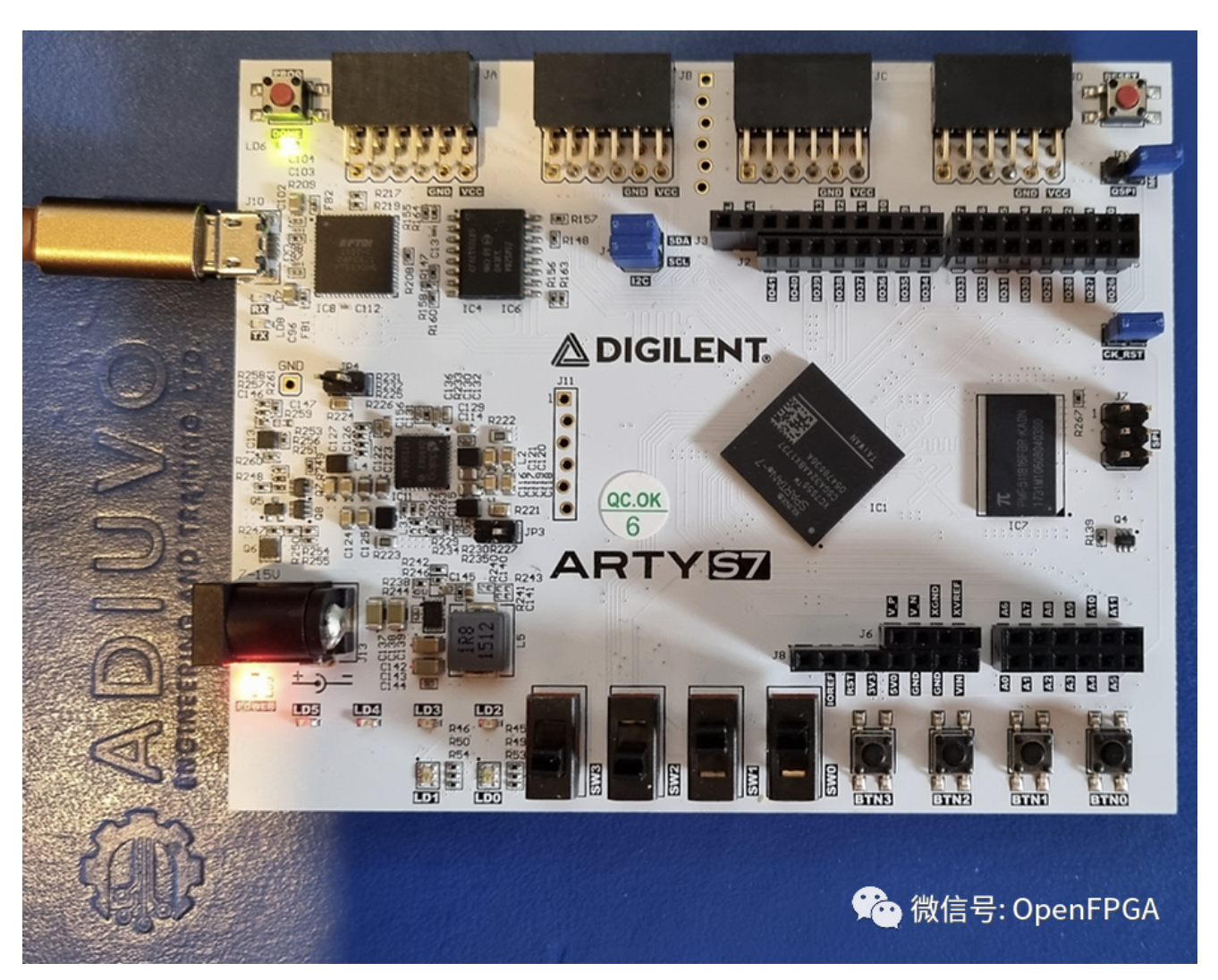

FPGA 的一大优势是我们可以实现并行图像处理数据流。虽然任务比较重,但是我们不需要昂贵的 FPGA,我们可以使用成本低廉范围中的一个,...

《优秀的IC/FPGA开源项目》是新开的系列,旨在介绍单一项目,会比《优秀的 Verilog/FPGA开源项目》内容介绍更加详细,包括但不限于综合...

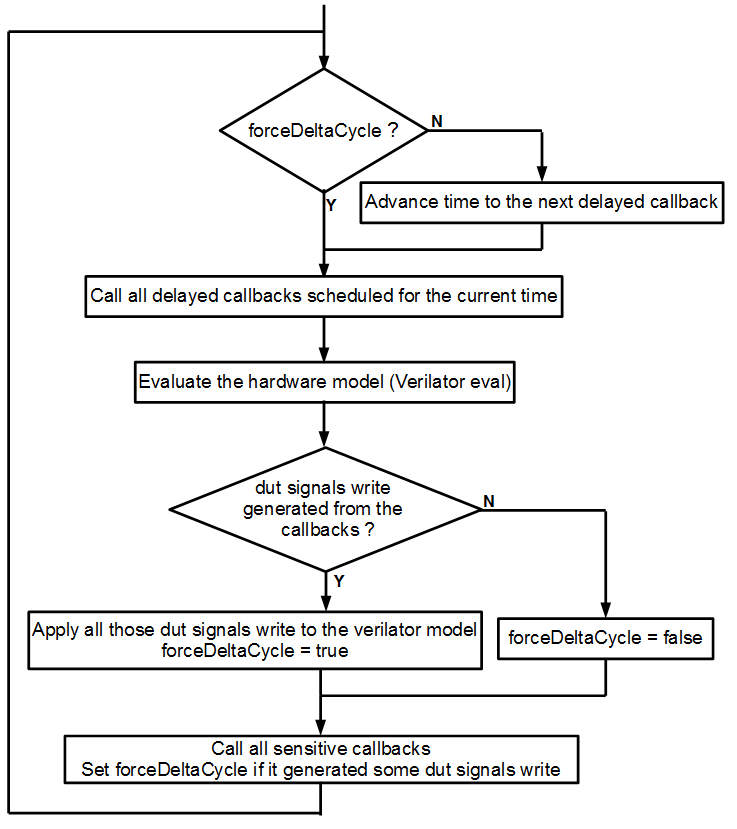

之后你可以调用compile(rtl)函数对硬件编译并为仿真器做准备。这个函数会返回SimCompiled实例。在这个SimCompiled实例中你可以用以下函...

Xilinx Vivado中提供了AXI FIFO和AXI virtual FIFO类似IP,这篇文章主要通过实例来讲解这两个IP的使用方法。

《优秀的IC/FPGA开源项目》是新开的系列,旨在介绍单一项目,会比《优秀的 Verilog/FPGA开源项目》内容介绍更加详细,包括但不限于综合...

在过去的十年中,可编程逻辑器件(PLD)市场不断增长,对PLD的需求不断增加。具有可编程特性且可编程的芯片称为PLD。PLD也称为现场可编...

之前介绍的项目《优秀的 Verilog/FPGA开源项目介绍(十四)- 使用FPGA实现LeNet-5 深度神经网络模型》最后我们分析了,纯FPGA实现神经网...

这一章会介绍SpinalHDL如何把名字从scala代码传递到产生的硬件中。知道这些能帮助你更好地了解如何保留名字, 以尽可能增加生成的网表的...

SpinalHDL编译器会做很多设计检查,来确保生成的VHDL/Verilog是可仿真的可综合的。基本上,SpinalHDL不会生成破损的VHDL/Verilog设计。...

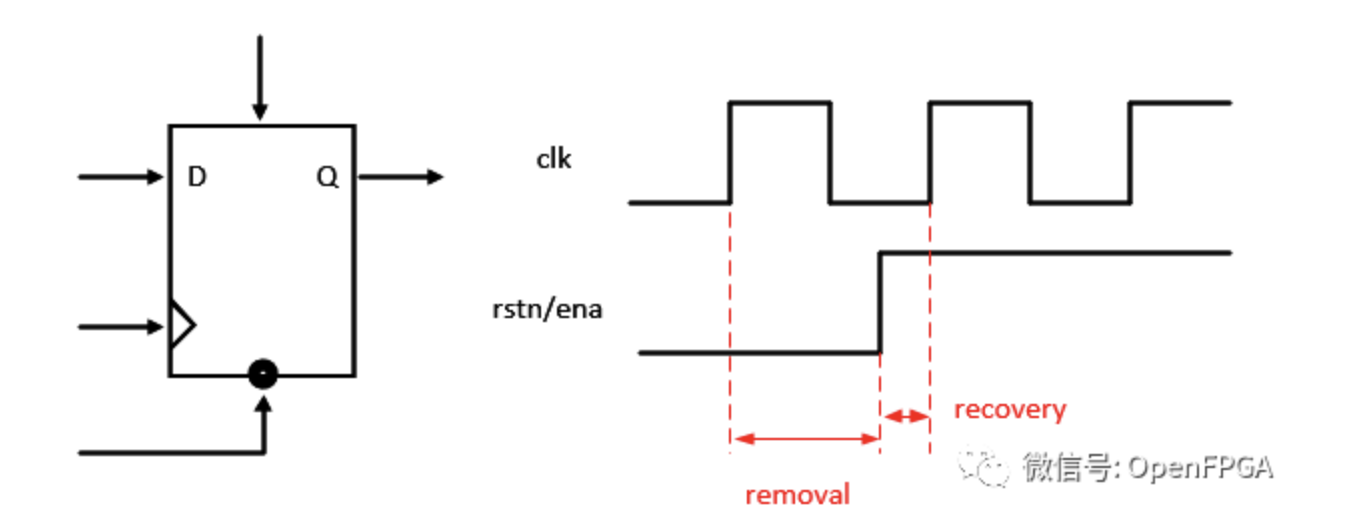

让我们从触发器开始,所有触发器都有一个围绕活动时钟沿的建立(setup time)和保持窗口(hold time),在此期间数据不得更改。如果该窗...

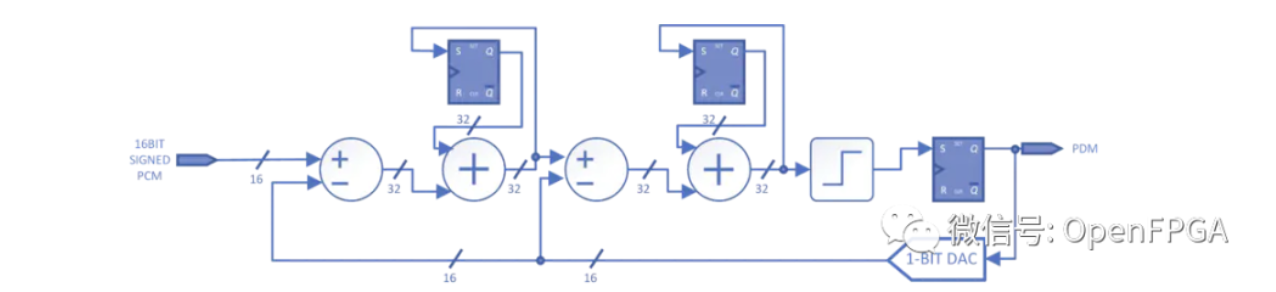

整个方案实现的原理主要是将PDM输出到FPGA管脚然后经过低通滤波接到比较器负端,Digital Filter换成累加器,就变成了真正的1-Bit ADC。...

SpinalHDL 是 Scala 语言的一个库,SpinaHDL 环境搭建所需的软件开发 Scala 需要使用 IDEA 软件;JDK17采用开源软件TencentKona-17.0.3....

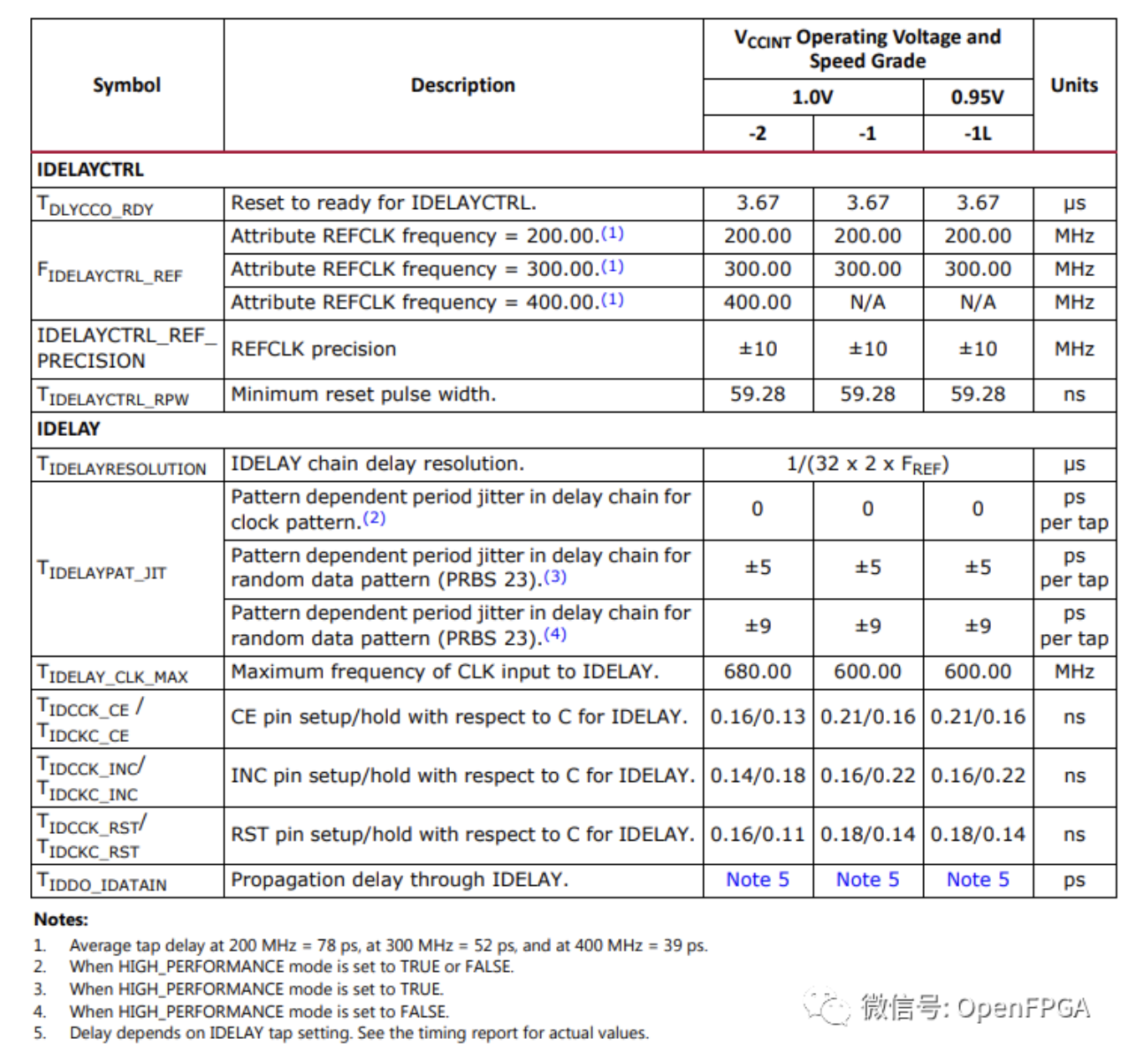

IO 灵活性是FPGA 最大的优点之一。如果我们设计的 PCB 信号走线不完美,IO的灵活性使我们能够对齐进入设备的高速数据,帮助我们摆脱困境。

当以太网接口的速率提升到100G以上后,用传统FPGA来实现对应的数据处理时,一定会遇到总线效率的问题。本文就分享团队对大位宽高速数据...

AXI总线在FPGA设计中使用越来越频繁,但初学的同学经常会因为对协议的理解不够深入,写出来的代码经常会出现死锁等问题,对FPGA设计与调...

IO 灵活性是FPGA 最大的优点之一。如果我们设计的 PCB 信号走线不完美,IO的灵活性使我们能够对齐进入设备的高速数据,帮助我们摆脱困境。