集微网消息 光刻机是半导体制造业中最核心的设备,光刻环节能实现芯片设计图从掩模到硅片上的转移。而光刻机工件台是光刻机的核心子系统...

集微网(文/Kelven)在集微网举行的第十期龙门阵当中,以“异构计算带来智能互联的下一个黄金十年”为主题,英特尔中国研究院院长宋继强作...

集微网(文/Kelven)自2014年《国家集成电路产业发展推进纲要》出台以来,政策的支持使得半导体行业飞速发展。从2015年开始,行业规模增...

【嘉德点评】粤芯在未来将聚焦于以生物检测芯片、视频监控摄像头芯片、红外测温芯片为代表的生物安全领域,弥补国产芯片制造业的短板。

集微网(文/Kelven)潮涨潮退,千禧年伊始中美蜜月的20年已过,美国对中国全面对抗的基调短期内是不会改变。在这一大环境下,以华为为代...

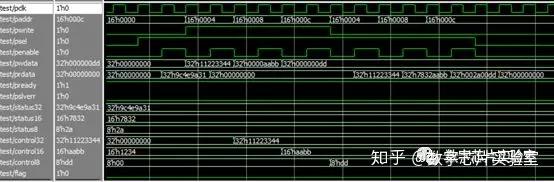

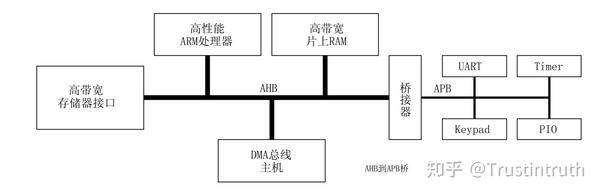

下面是一个APB slave 的verilog实例,大家可以在此基础上,设计自己APB slave接口的自定义模块控制器.

Scala在定义一个变量时,必须在其变量名前添加关键字“var”或“val”这两者的区别是“var”修饰的变量可以新赋值,并把原值抛弃,而用了“val”...

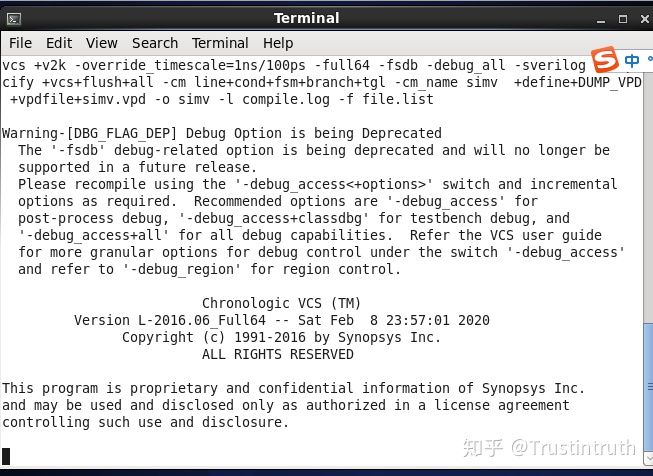

继上次使用VCS基础操作和makefile的书写,如果我们最后不使用vcs而是使用verdi该如何调用呢?和上次一样,我们同样要把我们的.v文件和tb...

make命令执行时,需要一个 Makefile 文件,以告诉make命令需要怎么样的去编译和链接程序。首先,我们用一个示例来说明Makefile的书写规...

1、基本逻辑运算、仅用与非或仅用与或非、最小项之和、最大项之积、卡诺图化简、逻辑门的mos管组成,笔试常出现

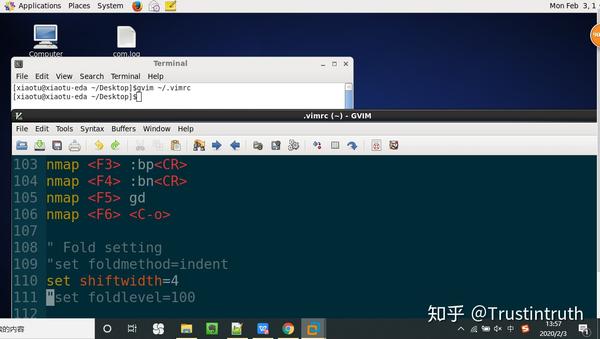

最近在学习Linux下的一些操作,在此总结gvim中的常用操作。由于许多命令用:开头,所以下面命令都是使用粗体文字。如有疏漏,还望指出。...

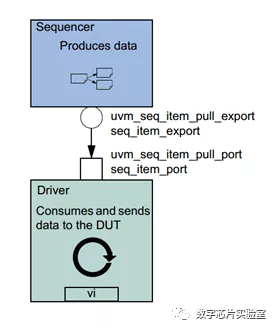

driver的作用是按照接口协议将事务对象驱动到总线。driver从sequencer中获取数据。UVM库提供了uvm\_driver基类,所有的driver类都应该直...

UVM库提供了uvm\_sequence\_item基类。 每个用户定义的事务对象都必须直接或间接地从这个基类派生。

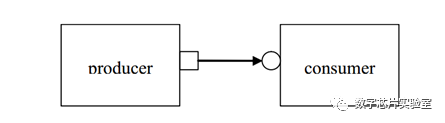

UVM提供了一组可用于连接各个组件的事务级通信接口。 TLM接口的使用将验证环境中的组件相互隔离开来。当RTL被修改时,UVM验证环境只需要...

由于项目中经常会涉及到总线的内容,想在AHB上挂一个SRAM和flash,我们从AMBA总线入手,从时序入手吧AMBA总线理解一遍。而这之中我们主...

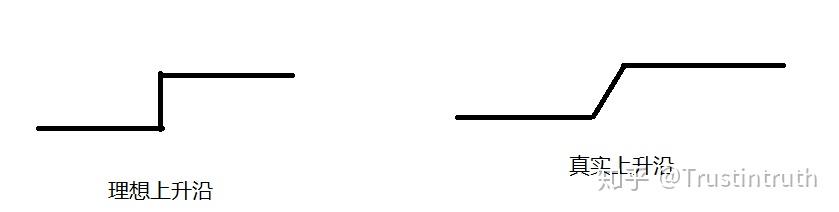

最近在做项目中遇到了一个问题,首先我们知道信号的边缘不会像我们想要的那么陡峭,而且不会像我们想的一样准时到达。作者:Trustintrut...

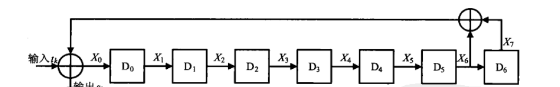

扰码是在数字传输系统中,对于数字信息进行随机化处理的一种技术,被广泛应用于通信各个领域。其作用是对数 据源发送的数字序列随机化处...

UVM提供了实现覆盖驱动验证(coverage-driven verification ,CDV)的框架。 CDV结合了自动测试向量生成,自检查和覆盖率收集,显著地缩...

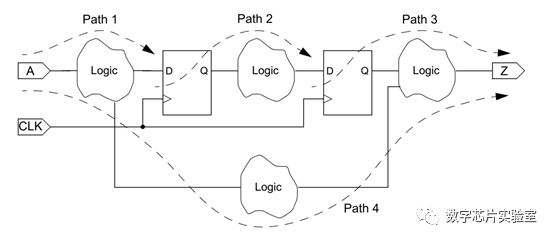

时序分析工具可以查找并分析设计中的所有时序路径(timing paths)。每条时序路径有一个起点(startpoint)和一个终点(endpoint)。

当设计中使用了多个时钟时,这些时钟域之间的关系可能是synchronous、asynchronous或者exclusive的。如下所示:Synchronous: