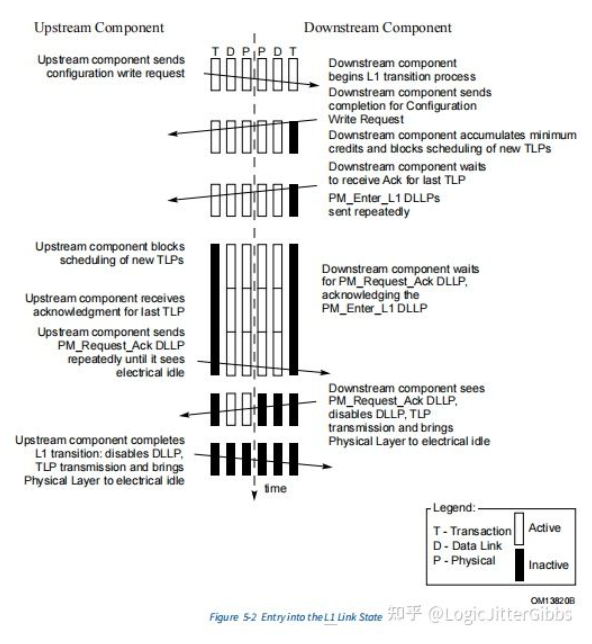

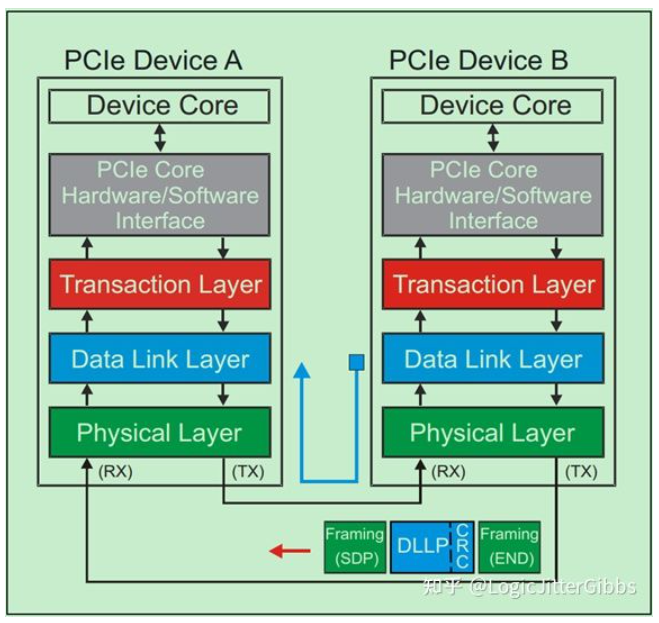

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.本文系转载,略做格式调整与增加解释(使用斜体表示),转自[链接]

• Global Platform Tech Studio(以下及后续简称GPTS)是针对GlobalPlatform智能IC卡(以下及后续简称GP卡)的安全域、安全通道、内容、...

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.本文系转载,略做格式调整与增加解释,转自[链接]

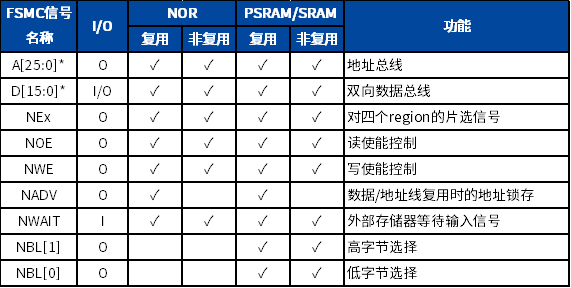

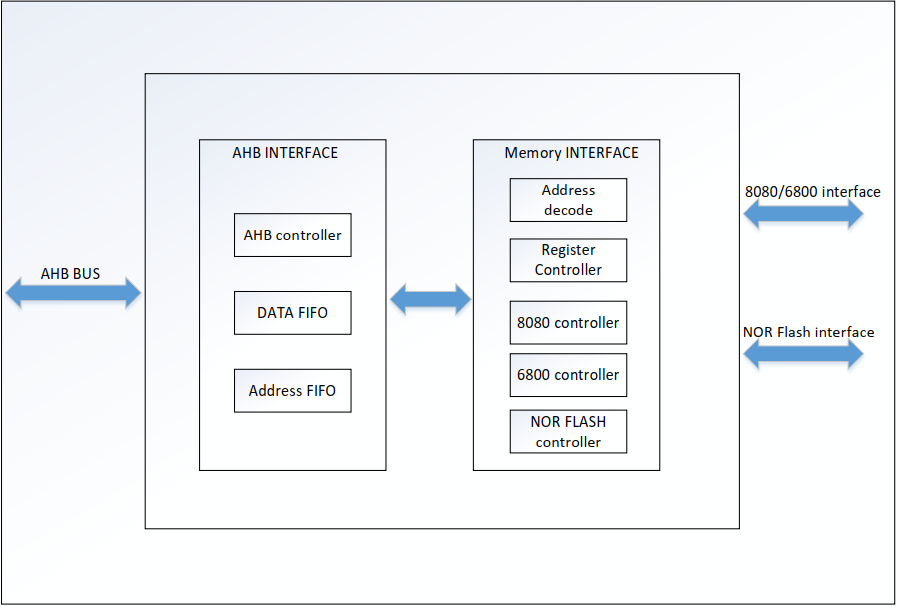

MM32系列微控制器为用户提供了丰富的选择,可适用于工业控制、智能家电、建筑安防、医疗设备以及消费类电子产品等多方位嵌入式系统设计...

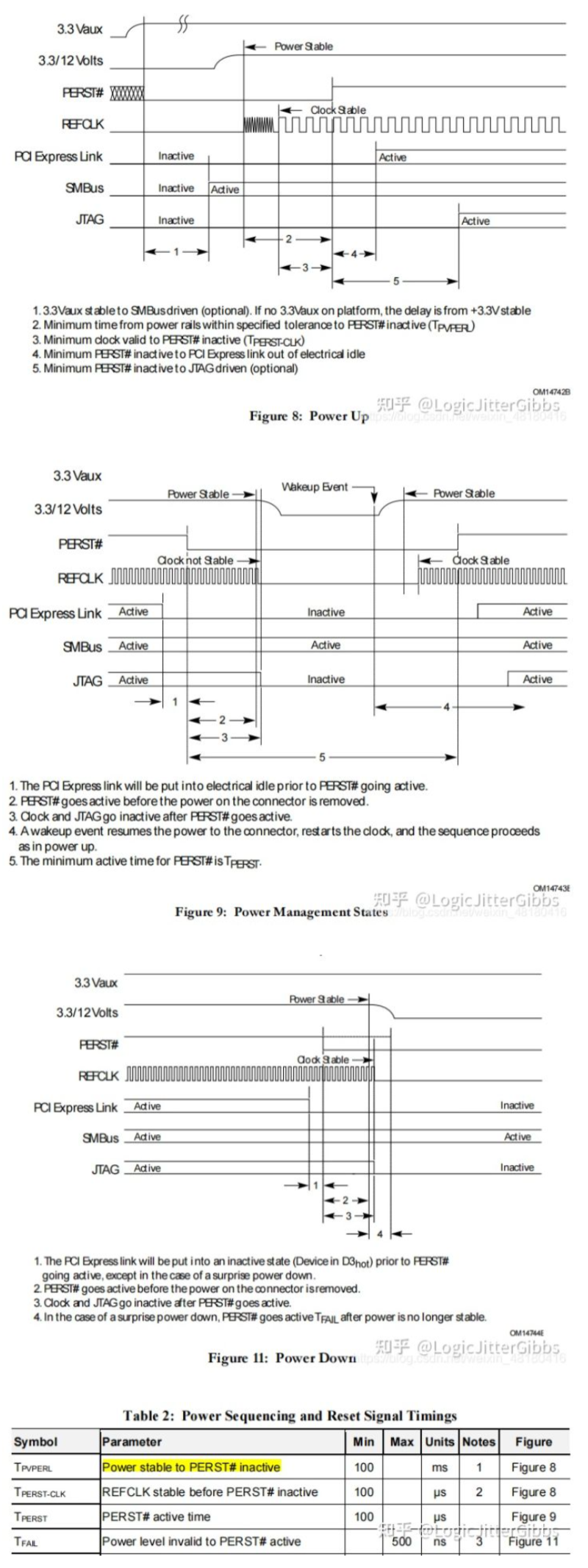

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.本文系转载,略做格式调整与增加解释,转自[链接]相应内容可参考:

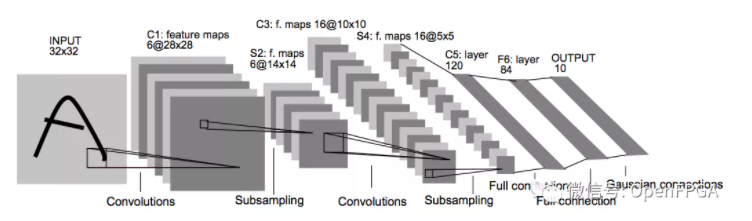

LeNet-5:是Yann LeCun在1998年设计的用于手写数字识别的卷积神经网络,当年美国大多数银行就是用它来识别支票上面的手写数字的,它是早...

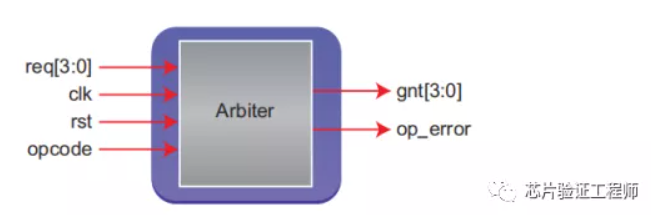

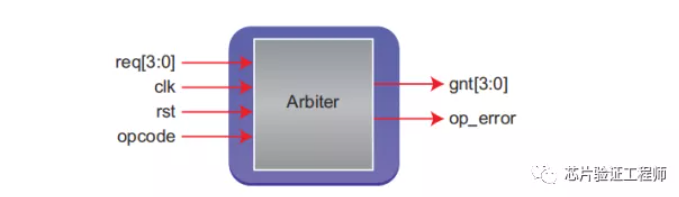

本文将使用一个简单的Arbiter(仲裁)设计示例展示SVA断言的概念和用法。 这个仲裁器有四个请求口req ,gnt信号指示哪个请求被授权。还...

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.本文系转载,略做格式调整与增加解释,转自[链接]相应内容可参考:

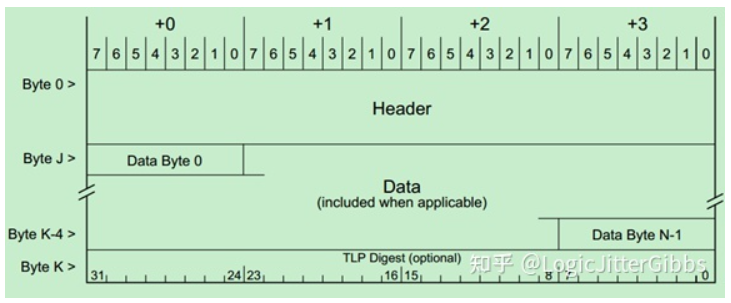

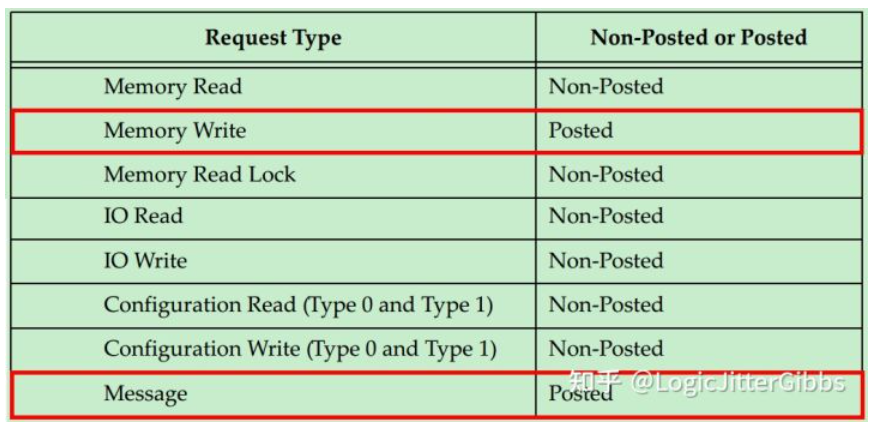

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.本文系转载,略做格式调整与增加解释(使用斜体表示),转自:PCIe扫盲...

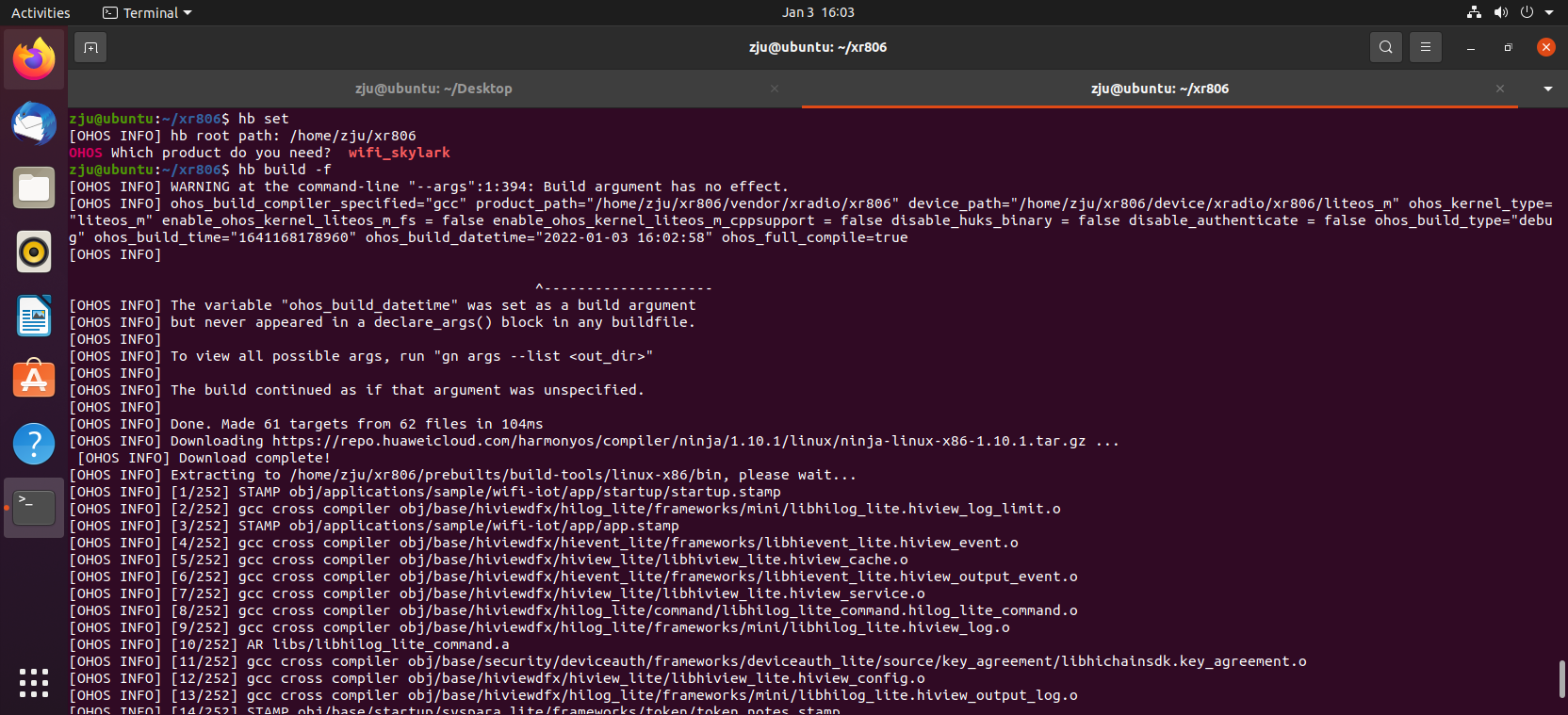

XR806体验一 安装一 安装流程XR806 鸿蒙系统的固件编译和固件烧录参考官方资料[链接]1. 获取鸿蒙分支代码:下载 arm toolchain {代码...}...

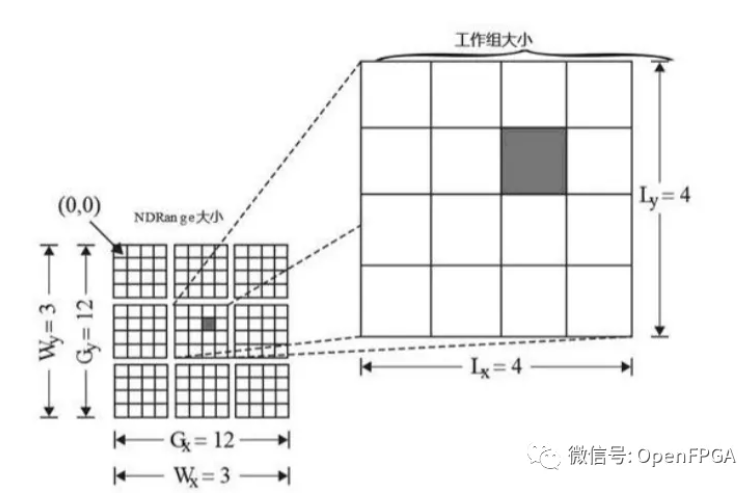

异构计算(Heterogeneous computing)技术从80年代中期产生,由于它能经济有效地获取高性能计算能力、可扩展性好、计算资源利用率高、发...

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.本文系转载,略做格式调整与增加解释(使用斜体表示),转自:PCIe扫盲...

交互式界面被越来越多地集成于多种应用中,例如医疗设备、过程控制、手机和其它手持设备。这些界面主要基于使用彩色LCD的图形HMI(人机...

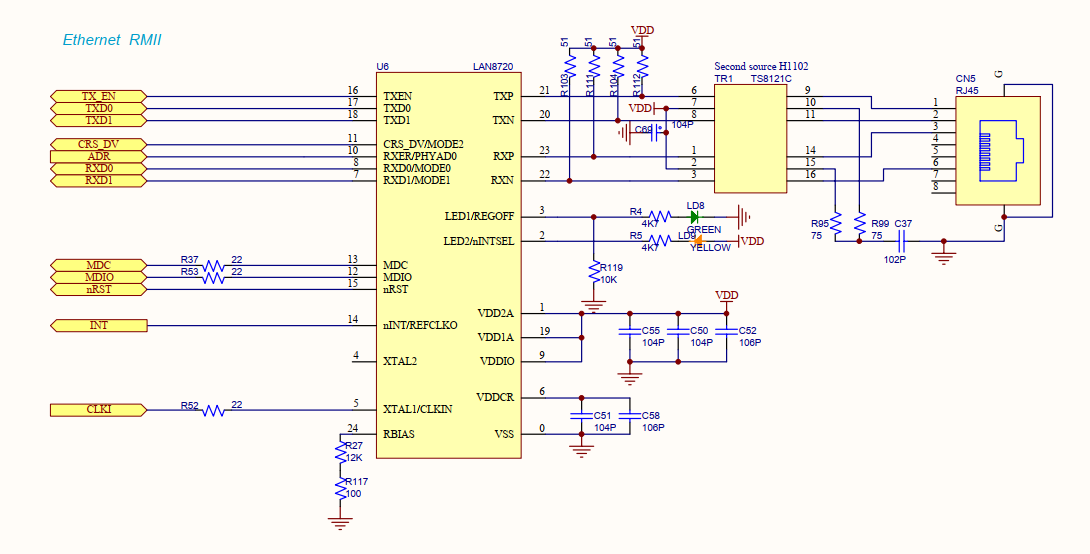

HTTP(Hyper Text Transfer Protocol超文本传输协议)是用于从万维网服务器传输超文本到本地浏览器的传输协议,它基于TCP/IP协议通信,...

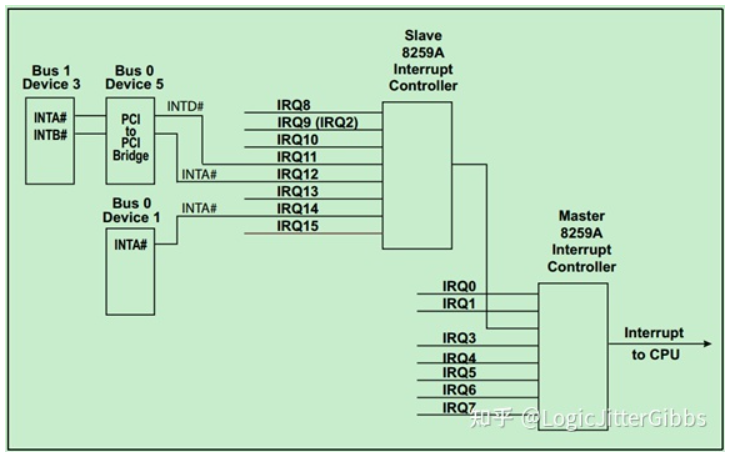

PCIe总线继承了PCI总线的所有中断特性(包括INTx和MSI/MSI-X),以兼容早期的一些PCI应用层软件。本次连载的文章只是简单的介绍PCIe中断...

在芯片设计中,ECO是指在经过布局布线工具后,将直接对门级网表逻辑进行修改的过程。因为马上就需要投片,没有足够的时间再进行布局布线...

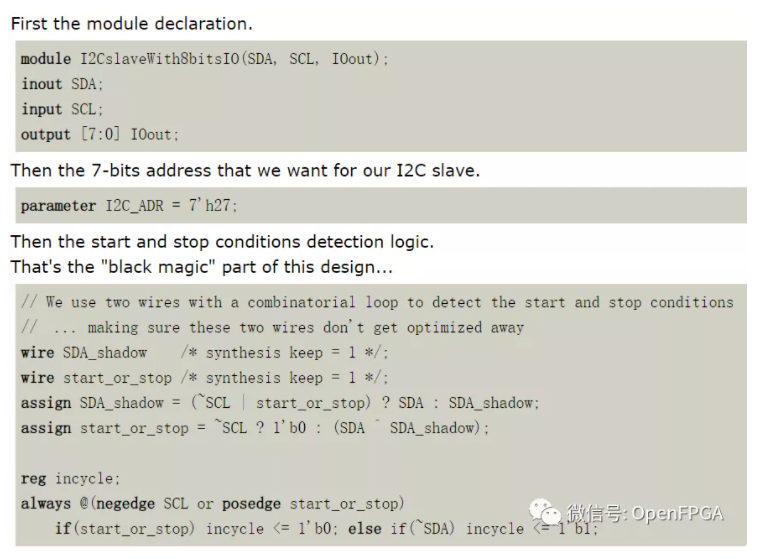

I2C 总线规范是由飞利浦半导体编写的。这家公司后来成为 NXP Semiconductors,现在它是 I2C 总线规范的维护相关者。

《看懂芯片原来这么简单》第15期快马加鞭地来啦!在上期漫画中,麒麟君向大家介绍了HMS Core中助力游戏开发的CG Kit,这期我们来看看负...

本文将使用一个简单的Arbiter(仲裁)设计示例展示SVA断言的概念和用法。 这个仲裁器有四个请求口req ,gnt信号指示哪个请求被授权。还...

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.本文系转载,略做格式调整与增加解释(使用斜体表示),转自:[链接]