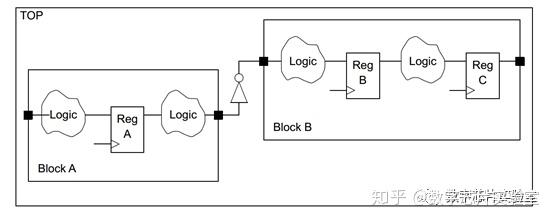

Physical design是将电路描述(circuit description)转化成物理版图(physical layout)的过程。在物理版图中规定cell的摆放位置和相互...

另外,在逻辑综合过程中,合理的设计划分(Design Partitioning),让综合工具充分优化设计中模块边界的时序和面积。

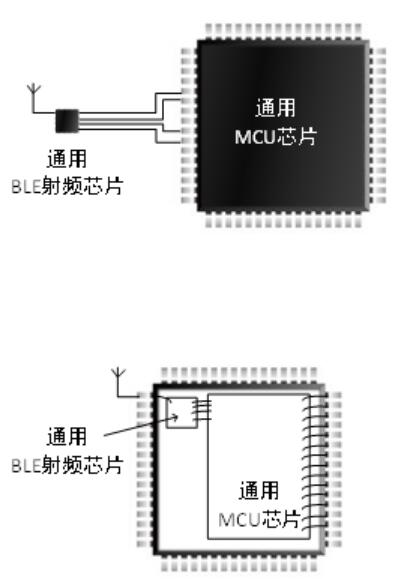

对于通用mcu芯片制造商来说,最大的挑战是保持差异化、高质量、解决方案能力和完善匹配的开发软件。差异化意味着mcu芯片的定义需要与市...

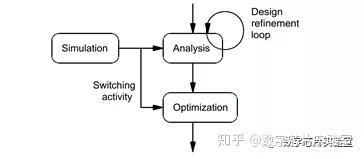

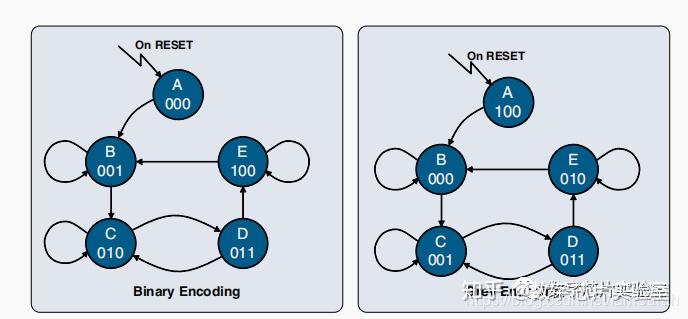

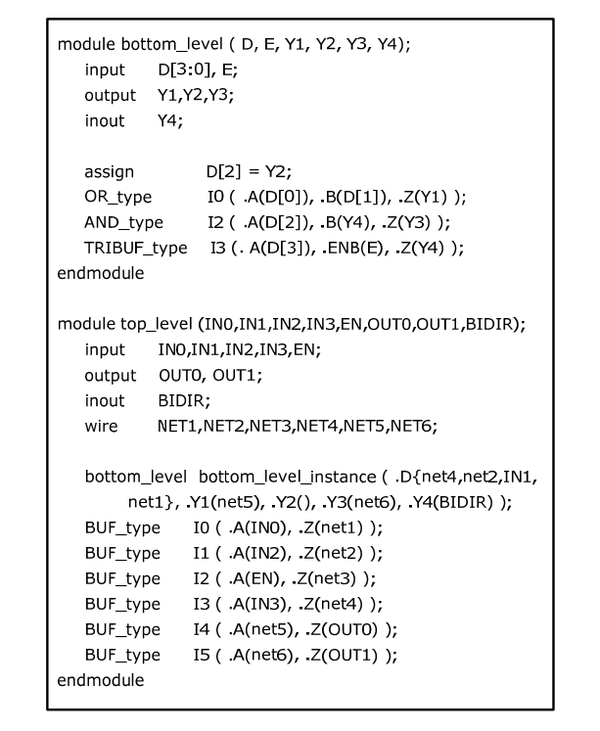

逻辑综合是设计从RTL到Netlist翻译优化的过程,类似于Design Compiler集成PrimeTime时序分析优化引擎,同样也集成了Power Compiler功耗...

7 月 22 日,深圳欢乐海岸,刚刚重启的电影院还没来得及上演轰动市民的大片,让整个电视界都兴奋的创维电视夏季新品发布会,在这里召开了。

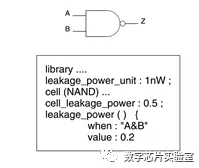

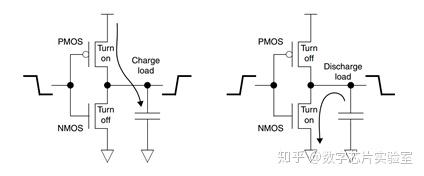

静态功耗是指逻辑门在不切换时消耗的功耗,其主要由源极到漏极亚阈值泄漏电流引起的,即逻辑门未完全关闭。因此,静态功耗通常称为泄漏...

IC Designer可以在设计的不同阶段采用基于Architectural或者Process的方法来降低功耗,设计者需要根据功耗、性能、成本和可靠性等因素折...

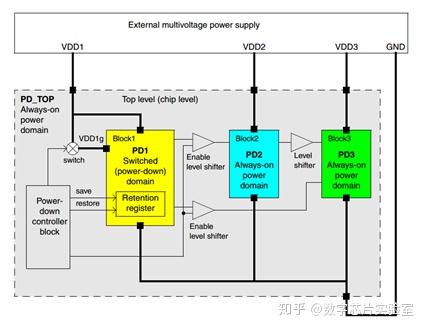

//来自微信公众号 "数字芯片实验室"UPF语言提供了一种指定设计电源要求的方法,但是没有明确说明如何实施这些要求。它不包含任何布局或...

随着工艺的进步,低功耗设计显得越来越重要了。作为一个数字前端设计师,我们就来看看如何在RTL级别降低功耗。

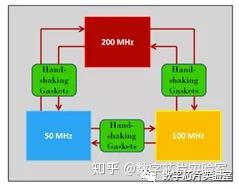

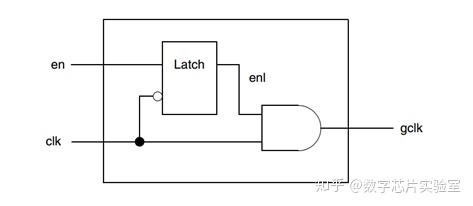

为了使用时钟门控,多电压域,多阈值库或电源开关等低功耗策略,工艺库必须包含支持这些策略的逻辑单元。 支持低功耗设计的一些单元包含...

凭借云计算的弹性扩容、按需使用、按量付费等优势,云数据中心正在蚕食传统数据中心的领地。据 Cisco 全球云指数测算,“到 2021年,94%...

【嘉德点评】粤芯在未来将聚焦于以生物检测芯片、视频监控摄像头芯片、红外测温芯片为代表的生物安全领域,弥补国产芯片制造业的短板。

在之前的IC设计中,关注的参数主要是性能(timing)和面积(area)。 EDA工具在满足性能要求的情况下,最小化面积。功耗是一个不怎么关心的...

在ASIC设计的早期,逻辑设计师使用原理图或电路编辑工具设计电路。随后,出现了两种硬件描述语言:VHDL、Verilog

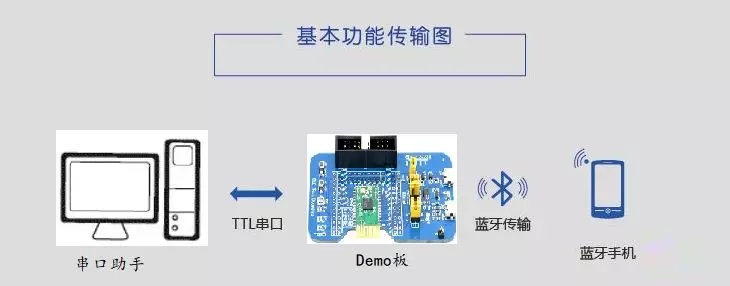

在前面一个章节中我们详细介绍了基于MM32W系列芯片的串口透传应用,该应用可以实现丰富的数据透传方案,在本章节我们将再给大家介绍一个...

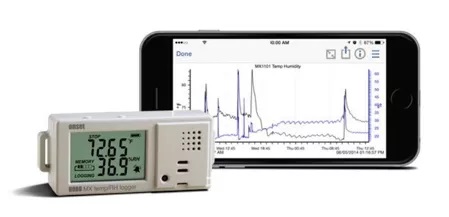

在前面一个章节中我们详细介绍到了基于MM32W系列芯片开发的使用场景非常丰富的简易蓝牙智能锁方案,在本章节我们将继续给大家介绍一个蓝...

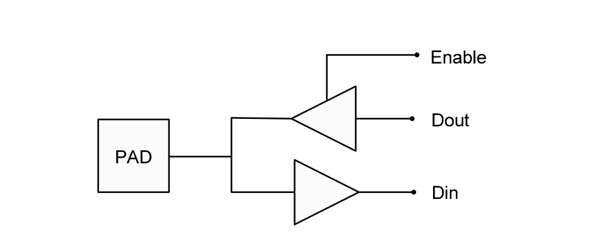

输入输出pad是ASIC后端设计中很重要的单元之一。I / O pad电路将ASIC core逻辑中使用的信号电平转换为ASIC外部的信号电平。同样,I / O ...

在前面一个章节中我们详细介绍到了基于MM32W系列芯片开发的温湿度监测仪方案,在本章节我们将继续给大家介绍一个使用场景非常丰富的蓝牙...

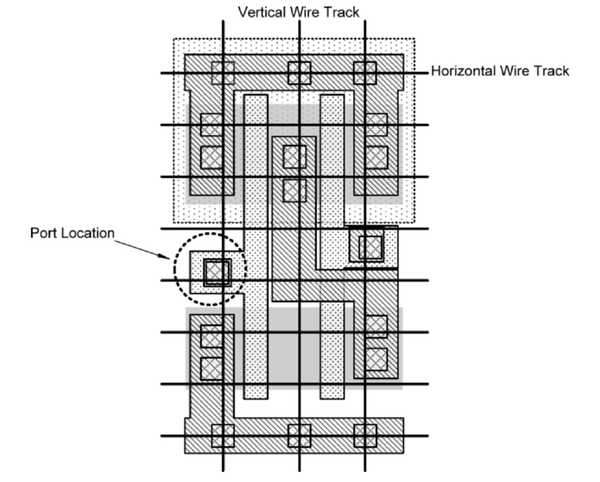

专用集成电路(ASIC)的数字后端设计需要各种类型的库。库是物理版图、抽象视图、时序和功能模型、晶体管电路描述的集合。

2017 年 3 月 22 日,美国福特车主多了一个福利——通过亚马逊 Alexa 语音平台就可以向星巴克订购咖啡。车主无需离开方向盘,就可以完成从...