相比外形奇特的 Galaxy Buds Live,三星新一代智能手表 Galaxy Watch3 发布后给人的惊艳并不多,甚至有一种似曾相识的感觉。

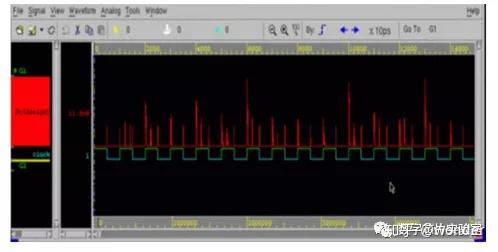

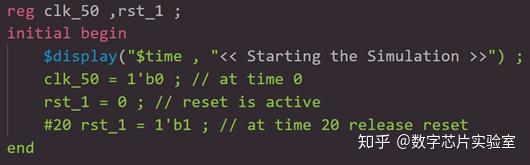

测试平台在早期通常需要具有调试功能,例如使用系统任务$monitor或$display打印指定的文本,以及在仿真过程中记录波形信息。

来自微信公众号 “数字芯片实验室”STEP 1: 编写Verilog设计和仿真文件• 建立一个新的文件夹,存放所有的项目文件• 编写设计文件Counter.v...

本实验将通过Formality GUI的方式展示形式验证基本流程,然后创建相应的Tcl脚本执行相同的形式验证流程。

语音助手大家并不陌生。苹果 Siri 初次亮相是在 2011 年 iPhone 4s 发布的时候;Google Assistant 则是在 2016 年的 Google I/O 大会上...

了解侧信道攻击(side channel attack)的同学可能清楚芯片的实时功耗和算法处理的数据是具有很强的相关性的,通过采集密码算法的实时功...

据调查显示,2019 年全国电梯注册量接近 700 万台,平均每台电梯每日载客量在 100 人次以上。

近日,IDC 等多家市场调研报告的数据显示,在 2020 年二季度全球智能手机出货量同比下降的情况下,华为首次以 5580 万部智能手机的出货...

PrimeTime PX支持两种功耗分析模式: averaged mode和time-based mode。在EDA工具的安装目录底下包含了这两种模式的Lab教程和相关设计文...

顾名思义,模拟/全定制设计流程用于设计模拟或者全定制电路。 全定制电路是指使用晶体管,电阻和电容设计的电路,但是全定制电路不一定...

Verilog-1995有两种基本数据类型:变量(reg)和线网(wire)。它们的值有4个状态:0,1,Z和X。这些变量可以用来存储组合逻辑值和时序逻...

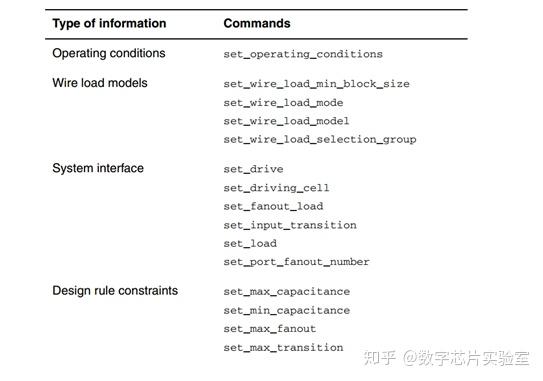

SDC(Synopsys Design Constraints)是一种基于Tcl的格式。 SDC文件中的所有命令都符合Tcl语法规则。

Milkyway database is a unifying design storage format for tools in the Synopsys Galaxy™ Design Platform, including Design Compi...

设计完数字系统后,通过仿真进行逻辑功能验证非常重要。在Verilog中,可以编写testbench(测试平台)以验证代码。下面是编码testbench的一...

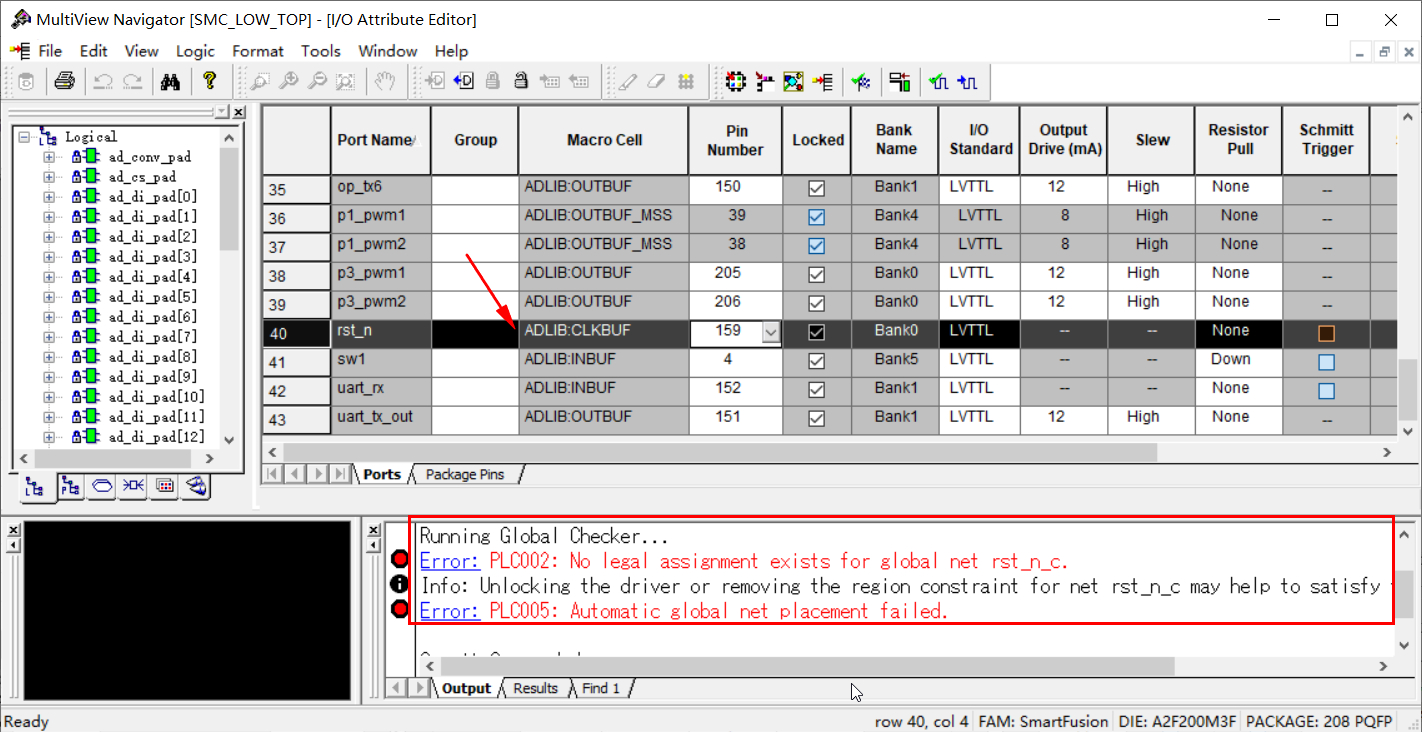

刚开始做Microsemi FPGA+SoC开发时,会用到几个ARM专用的IP Core,功能一复杂起来,就会遇到某些信号如rst_n不能分配到指定的引脚上的情...

•行为级(Behavior Level):通过行为级算法描述数字系统。•寄存器传输级(Register Transfer Level):在寄存器传输级,通过寄存器之间...

最近在GitHub又发现了一个嵌入式软硬件都开源的项目——基于STM32G0的锂电池快充充电器,使用Type C接口的充电头供电,支持为1s - 4s锂电...

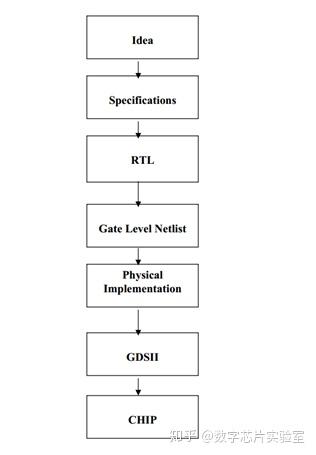

要设计芯片,需要知道想要设计芯片的内容(Idea)。 在ASIC设计流程中的每一步,Idea都在不断地改变着表现形式。 ASIC设计流程的第一步就...

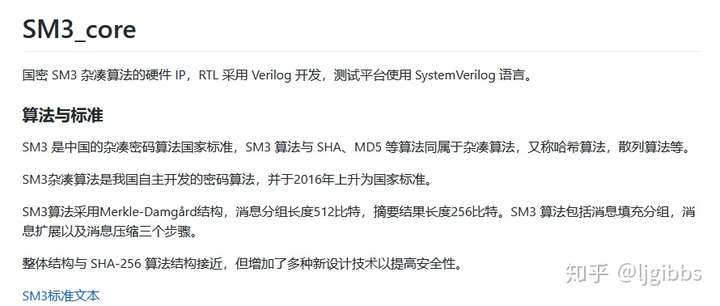

国密 SM3 杂凑算法的硬件 IP,RTL 采用 Verilog 开发,测试平台使用 SystemVerilog 语言。

ASIC是专用集成电路(Application Specific Integrated Circuit),也就是说如果我们为特定应用设计集成电路,则称为ASIC。但是,存储器...