run_phase和main phase都是task phase,且是并行运行的,后者称为动态运行(run-time)的phase。如果想执行一些耗费时间的代码,那么要在...

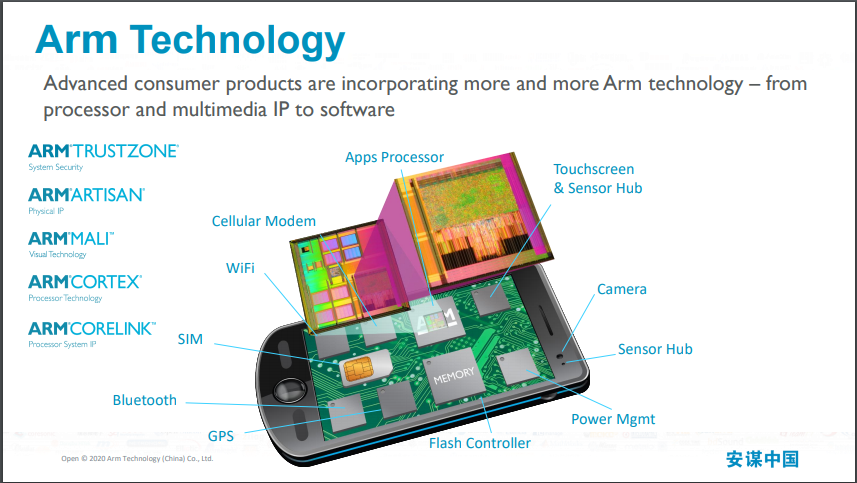

Cortex-M处理器家族日益壮大,大家可以根据自己的需求灵活选择,但是如何精准挑选合适的CPU 处理器IP也是困扰大家的问题,此次邀请到安...

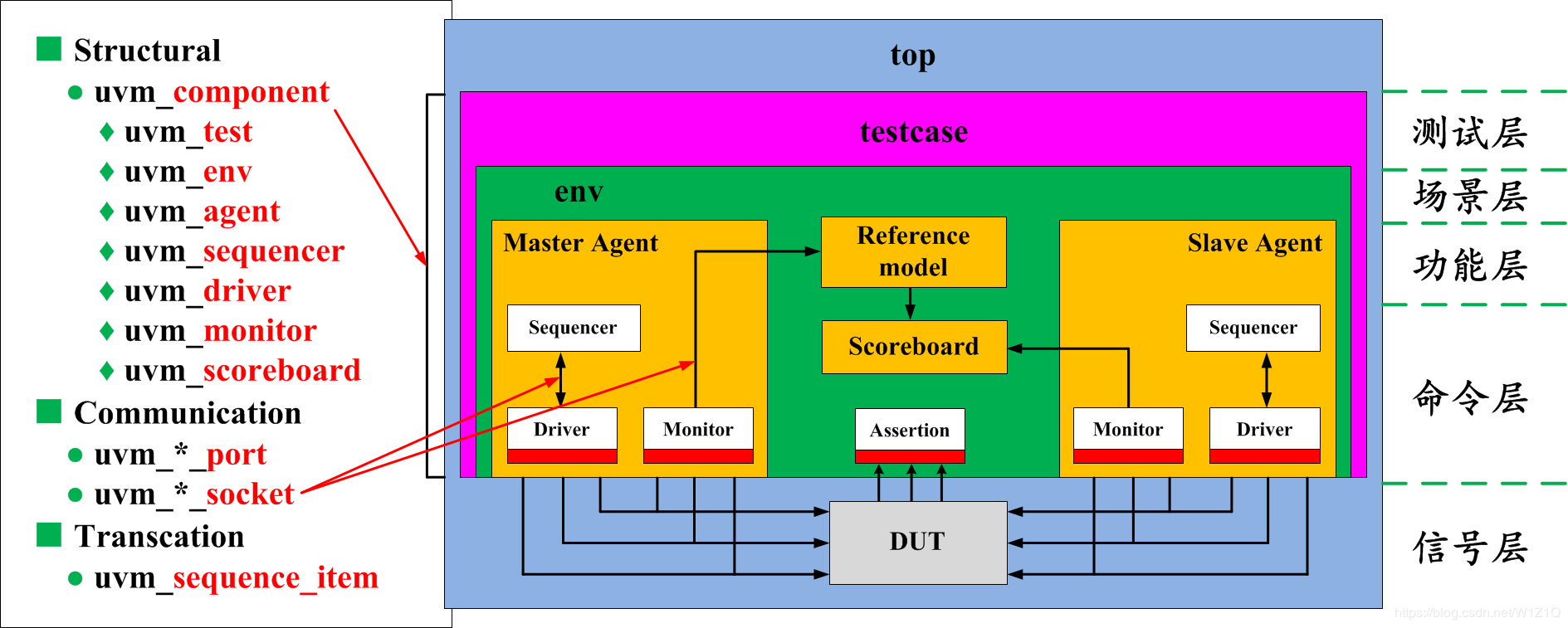

对于验证方法学来说,分层的测试平台是一个关键的概念。虽然分层似乎会使测试平台变得更复杂,但它能够把代码分而治之,有助于减轻工作...

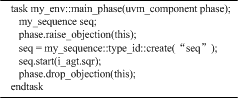

第一种(手工启动):在某个component的main_phase中启动sequence,如以my_env和my_sequencer为例:

随着北斗三号全球卫星导航系统GNSS日前的正式开通,自1983年立项研究,1994年开始建设,到2020年完成,耗时37年、北斗“三步走”发展战略...

事情缘由2020年8月7日,在中国信息化百人会2020峰会上,华为消费者业务CEO余承东对外表示,因为美国第二轮的制裁,华为自研的旗舰芯片麒...

Arm中国2021校园招聘正式开启,IC设计工程师,软件工程师等岗位需求多样。2021届的毕业生们,速速投递你的简历,与我们一创造中国智能科...

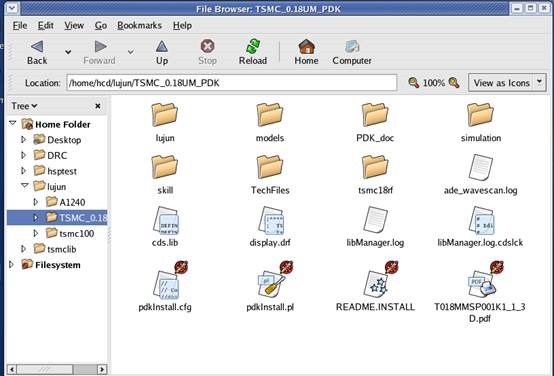

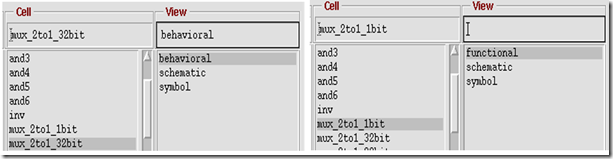

这里用的库是TSMC_0.18UM_PDK,0.18的库。从eetop下载的库。此库只可用于学习用。

VCS是synopsys的仿真verilog的仿真器。基于linux系统。有命令行模式和图形化模式。图形化模式是用的dve。

集微网(文/Kelven)如同钢铁是工业社会的粮食一般,类比过来,集成电路会是当今信息产业的粮食和动能。

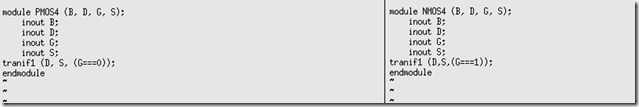

对于一个MOS电路来说,计算的话,有两个参数是比较重要的。一个是vth,一个是UnCox。不考虑其他效应。

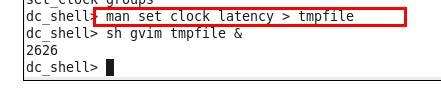

DC中,约束的时候,需要添加关于latency的约束。约束latency的命令是set_clock_latency。使用man命令,查看。这里,有个技巧,可以将man...

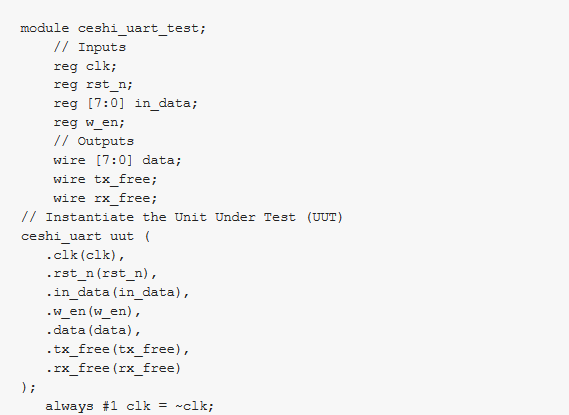

在cadence中,使用mos管和电阻构建了数字电路,但是要对这电路进行功能仿真,仿真的激励也比较复杂,不能使用简单的信号源产生,这个时...

NC可用于数模混合仿真,即用verilog语言给画的电路图添加输入激励信号,然后查看输出信号,以验证电路是否正确。。

如果安装的是modelsim 10.4版本的话,软件已经将UVM的库给编译好了,生成了.dll文件,供UVM验证使用。

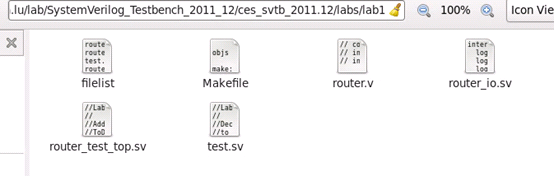

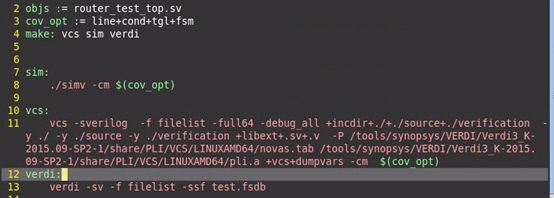

对于编写的systemverilog代码,在linux下,可以使用vcs编译,但是编译的时候,要注意,要加入几个选项。

对于vcs工具,支持生成覆盖率报告,通过查看覆盖率报告,即可知道设计中有什么问题。要生成覆盖率报告,要在编译和仿真的时候,加入一个...

综合作为后端设计中承上启下的一个环节,连接前端设计与后端PR的环节,在整个后端设计领域中占据非常重要的位置,决定了后端设计最终能...

集微网消息 光刻机是半导体制造业中最核心的设备,光刻环节能实现芯片设计图从掩模到硅片上的转移。而光刻机工件台是光刻机的核心子系统...

本文介绍CHI协议中的Cache Stashing操作和DVM操作,将分为两章节来描述。作者:谷公子