对于图1所示TX/RX模拟部分的实现方式,大家是不是一直有这样的疑问: Serdes在将并行data通过DAC串行发出去的时候,或者在接收端通过ADC...

在ASIC设计中,我们使用FIFO或者RAM的时候经常会用到校验位,例如奇偶校验或者ECC(海明码)校验,当然,也有可能不使用任何校验位。那...

感谢剑来接受采访,与剑来认识5年多,剑来在工作中很认真,也是一位非常优秀的工程师。本次采访主要聊了下剑来从刚毕业,到做Block,PR/...

Common Refclk Architecture,即同源参考时钟架构,PCIe收发设备共用一个时钟源,是目前是使用最为广泛的方案。

Serdes RX通过CDR的PD(数字鉴相器)来提取相位信息,然后调整DCO(数字压控振荡器)的输出相位来实现数字时钟恢复,如图1所示。一般判...

在芯片内部,信号一般都是通过并行传输的,因为串行传输实在是太慢了。然而芯片的IO都是串行传输的,并行传输对于硬件布局实在要求太高...

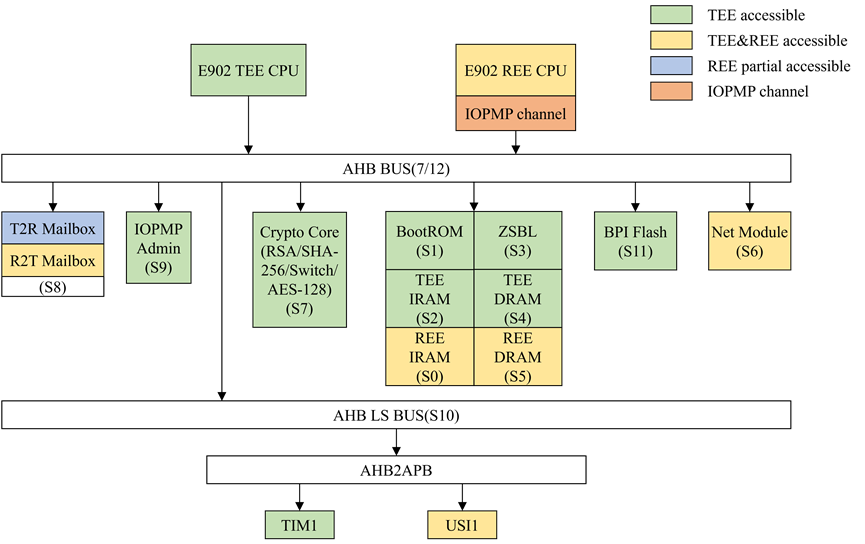

本文为2023年第七届全国大学生集成电路创新创业大赛(“集创赛”)芯原杯一等奖作品分享,参加极术社区的【有奖征集】分享你的2023集创赛...

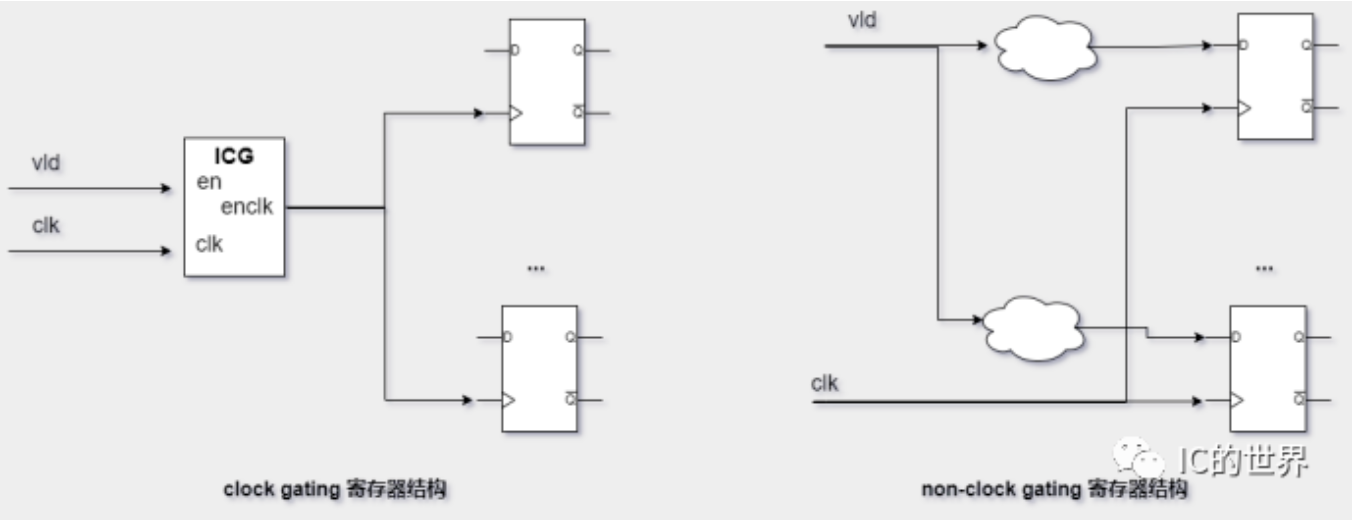

在ASIC设计中,项目会期望设计将代码写成clk-gating风格,以便于DC综合时将寄存器综合成clk-gating结构,其目的是为了降低翻转功耗。因...

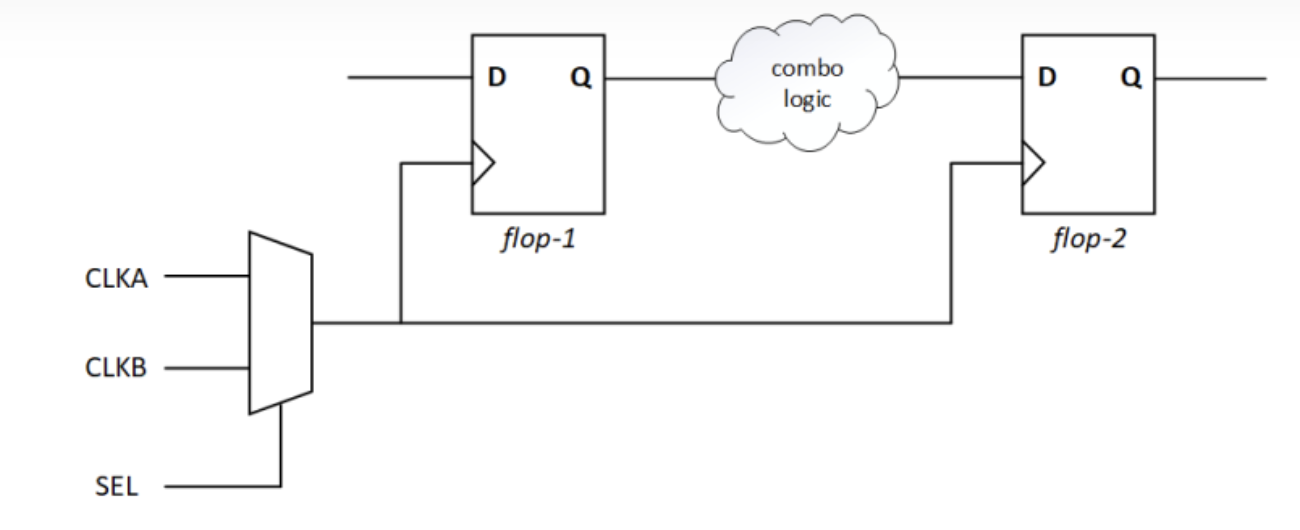

本文基于VC_SpyGlass_CDC_UserGuide整理了3种常见的cdc(Clock Domain Crossing)错误。需要注意的是:

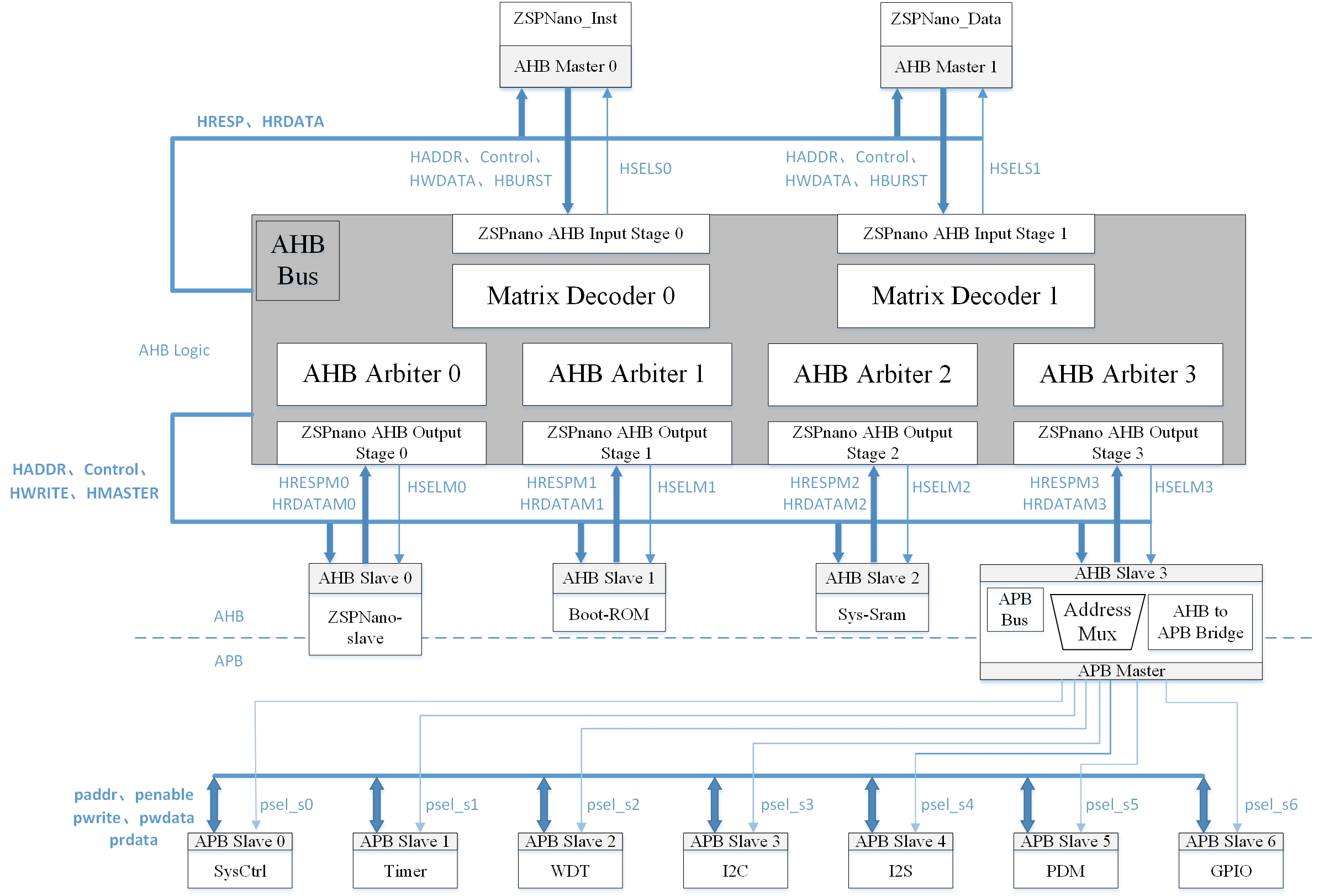

本文为2023年第七届全国大学生集成电路创新创业大赛(“集创赛”)平头哥杯一等奖作品分享,参加极术社区的【有奖征集】分享你的2023集创...

如下代码所示,在verilog代码中,无复位寄存器是没有复位信号的。在12mn,7mn,5mn工艺中,同类型的标准cell,无复位cell比有复位cell面...

TimeGen 是一款图形界面的波形绘制软件,使用鼠标进行操作,广泛应用于IC设计、硬件设计、集成电路等领域,安装在windows系统中。TimeGe...

相约艾睿电子技术解决方案展,探讨科技无限可能相约艾睿电子技术解决方案展,探讨科技无限可能相约艾睿电子技术解决方案展,探讨科技无...

在ASIC设计或者FPGA设计中,我们常常使用异步fifo(first in first out)(下文简称为afifo)进行数据流的跨时钟,可以说没使用过afifo...

本文是 how to define Synthesis timing constraint 系列文章的第六篇。

旗舰板卡0元用!飞凌嵌入式「RK3588开发板产品体验官」限时招募旗舰板卡0元用!飞凌嵌入式「RK3588开发板产品体验官」限时招募旗舰板卡0...

本文是 how to define Synthesis timing constraint 系列文章的第五篇。

先看一段代码 请根据这段代码写一个assertion检查 count 每次加5。 下面是一种写法 看起来不算太复杂。 但是如果让你写一个关于fifo 不...

在芯片设计过程中,通常会针对特殊情况导致芯片无法使用额外添加一些功能,使得芯片具有更好的抗干扰能力。自恢复设计应用场景很广泛,...

在数字系统级别的时钟域交叉(CDC)中,亚稳态传播问题是一个重要的挑战。在这个问题中,由于时序差异,信号在触发器之间的传输可能会导...