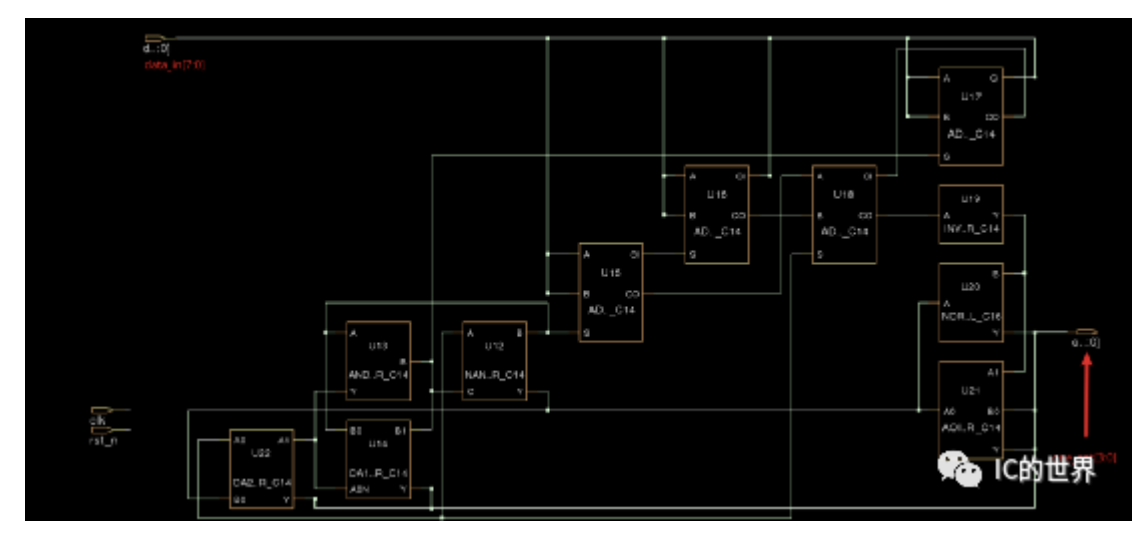

如下图,当master发起mem读请求后,收到读返回数据时,进行超时判断,如果超时,则数据丢弃,如果没有超时,则数据正常接收。

这篇文章介绍下BASH shell中的字符串处理的相关命令。之前有介绍过shell的其它命令,请参考:

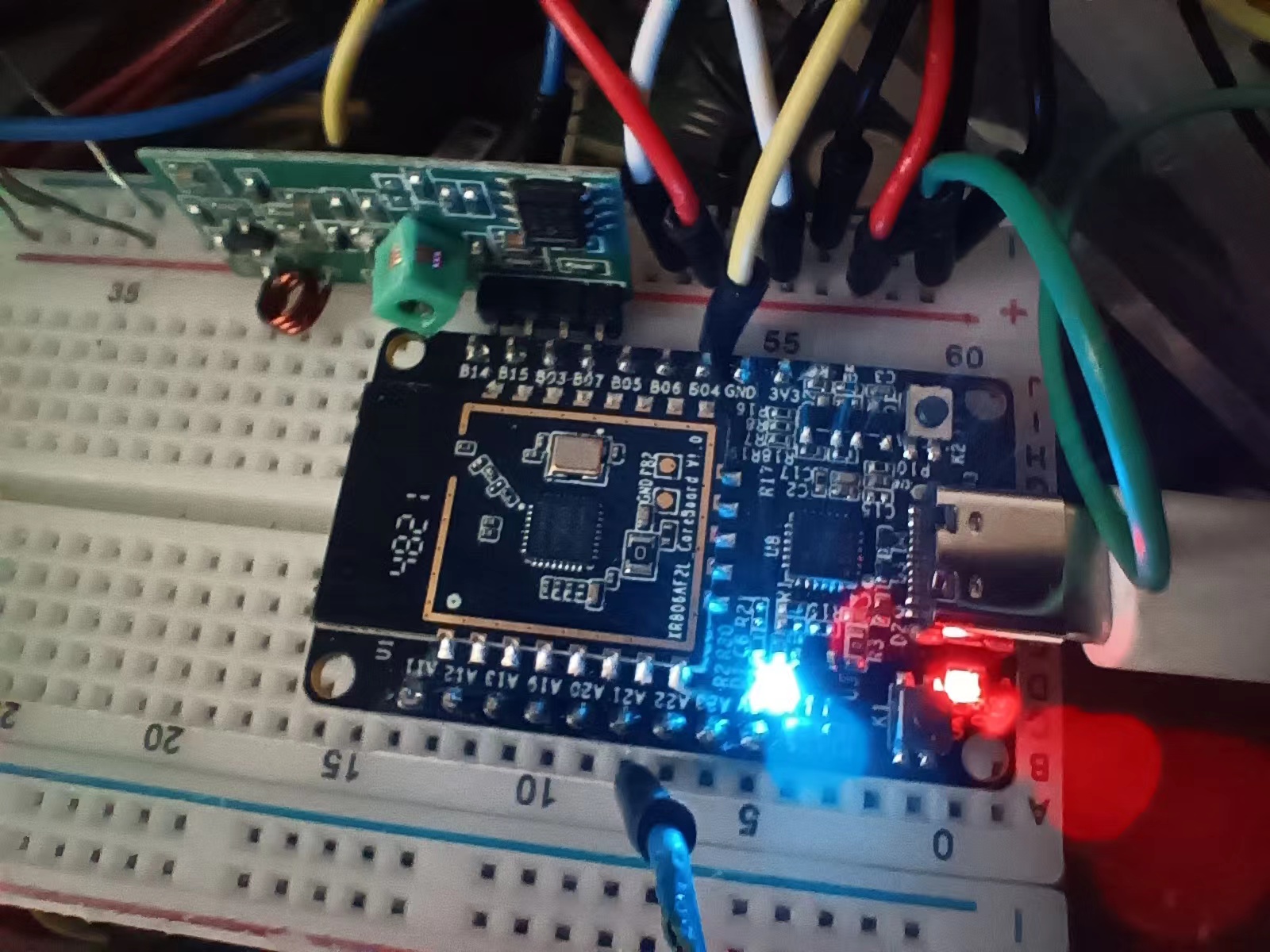

非常感谢基于安谋科技STAR-MC1的全志XR806 Wi-Fi+BLE开源鸿蒙开发板试用活动!非常感谢极术社区!非常感谢极术小姐姐!非常感谢全志在线...

这篇文章介绍下BASH shell中的条件相关的命令,包括:if, case, while, until, for, break, continue。之前有介绍过shell的其它基本命令...

非常感谢基于安谋科技STAR-MC1的全志XR806 Wi-Fi+BLE开源鸿蒙开发板试用活动!非常感谢极术社区!非常感谢极术小姐姐!非常感谢全志在线...

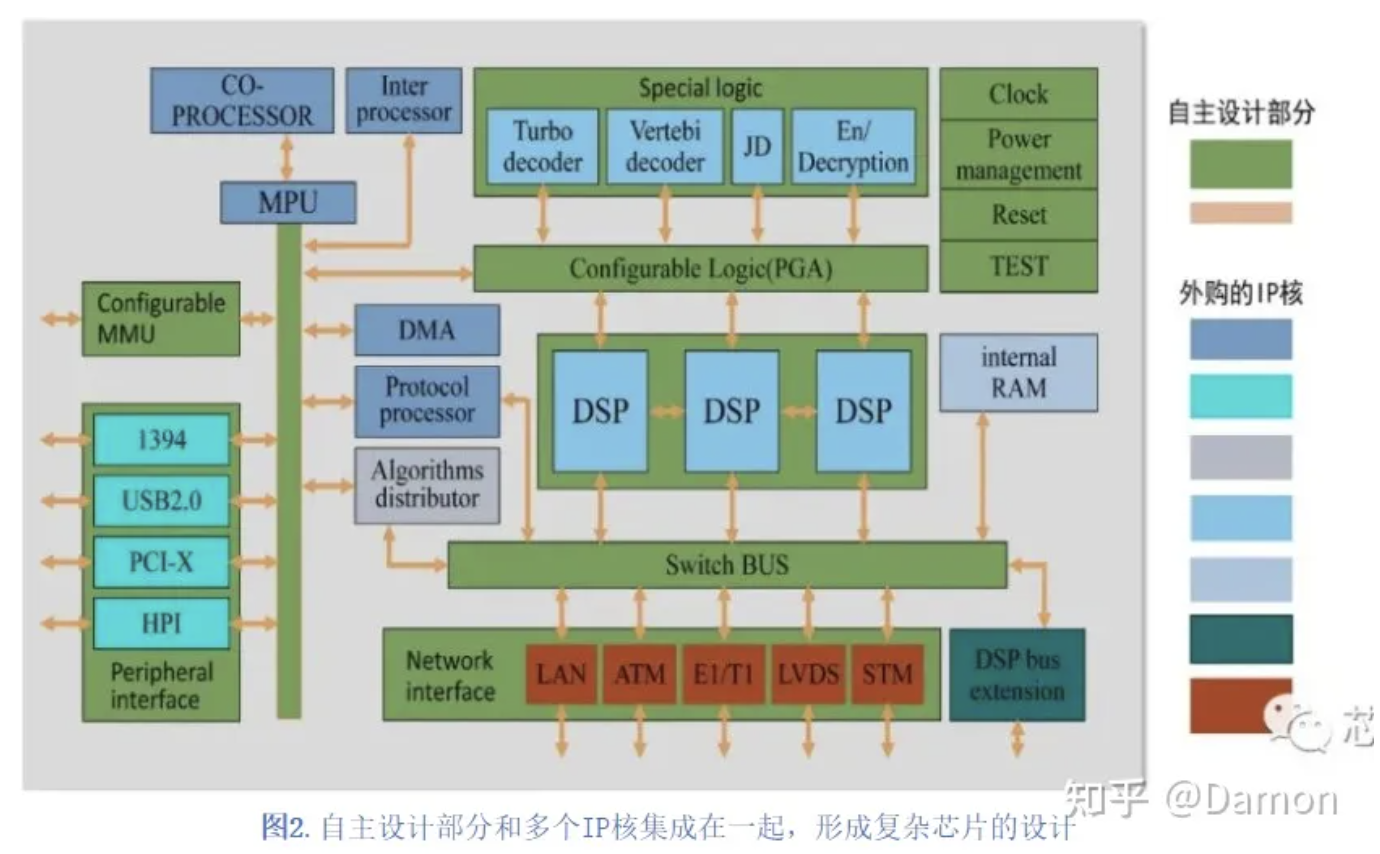

IP一般指IP核,是芯片中具有独立功能的电路模块的成熟设计。该电路模块设计可以应用在包含该电路模块的其他芯片设计项目中,从而减少设...

采用for循环语句,逐个bit位判断是否为1,为1则累加,否则保持不变,最终输出输入信号中1的数量。

在软件硬件交互的过程中,通常需要软件(host)对特定地址的寄存器进行写操作,告之硬件进行特定的处理流程,我们在《IC设计:软硬件交...

去年以独角兽Argo AI公司倒闭为代表,自动驾驶进入寒冬,但也让那些有着长远谋划的企业沉下心来,脚踏实地搞技术、做产品。今年随着人工...

9月21日,东芝公司表示,以日本国内基金“日本产业合作伙伴”(JIP)为主的财团通过收购邀约,已累计取得其超过三分之二的78.65%股份。东...

在理想的世界里,我们希望验证芯片的每一种可能的排列组合。 但在大多数情况下,这根本不可能。即使是一个看似简单的模块,也可能有成百...

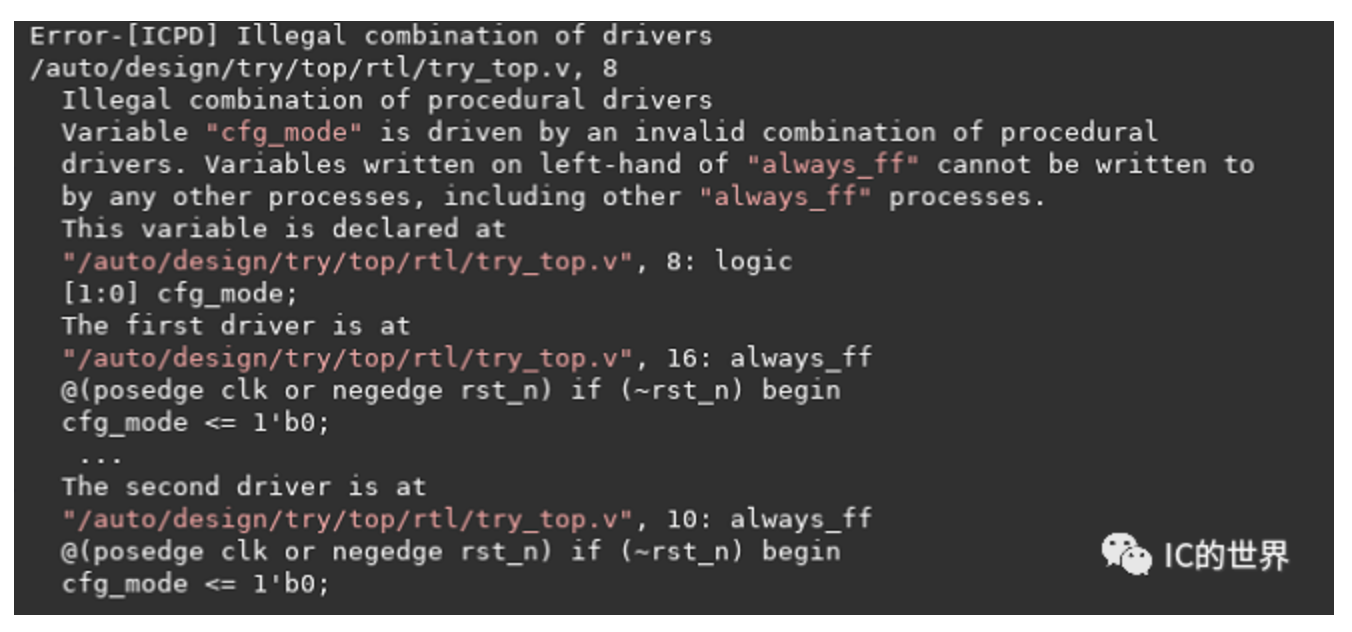

在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是lo...

当恩智浦半导体开始使用先进的低功率芯片设计技术时,有一件事令其大吃一惊。“某些情况下,在实现阶段出现了两倍的产能下降。”NXP公司设...

在设计中,我们经常会用到RR(Round-Robin,RR)轮询调度,用于保证在一个时间段内的多个请求信号都能得到公平响应。

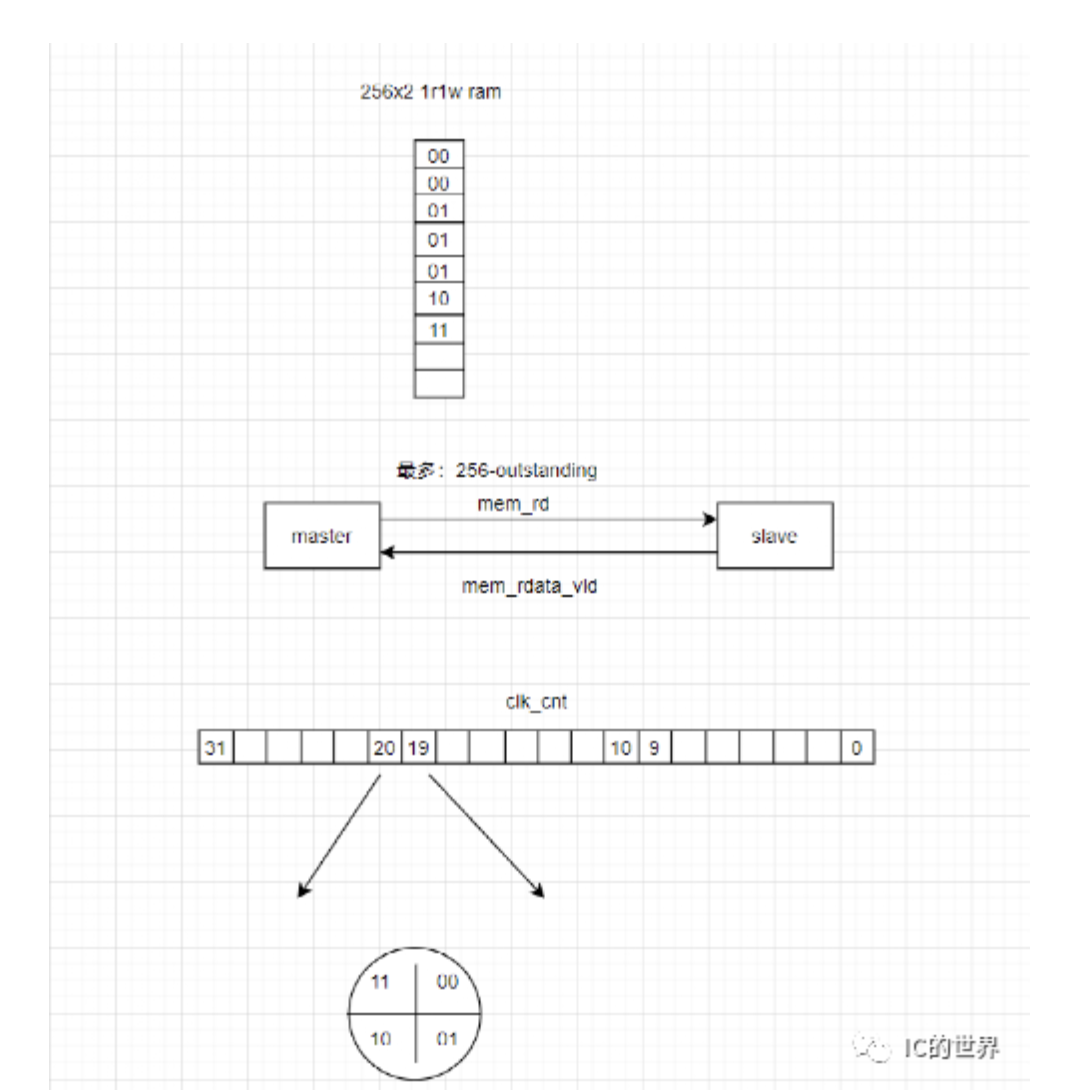

在芯片设计中,常常有这样的应用场景。硬件给软件传递消息,软件通过polling的方式获取。在我们的案例中,我们约定,硬件每次都上送128b...

因为一个SoC产品不只包括硬件,而是软件和硬件的结合。在很多的SoC中,软件设计的复杂度和开发周期都要超过整个硬件的设计。软件设计在...

Crossbar是一种交换结构,它由多个输入端口、多个输出端口和一个开关矩阵组成。以下是对Crossbar各个组成部分的详细介绍:

第八章 控制和状态寄存器略,与DVSEC相关的寄存器描述。不想再解释什么是DVSEC了。第九章 复位,初始化、配置和可管理性9.1 CXL启动和...

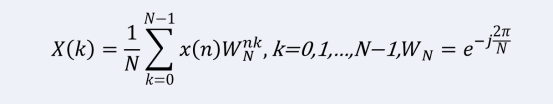

了解FFT的作用,掌握FFT 算法的算法原理、计算量和算法特点,实现FFT算法并通过CCS图形窗口查看结果。

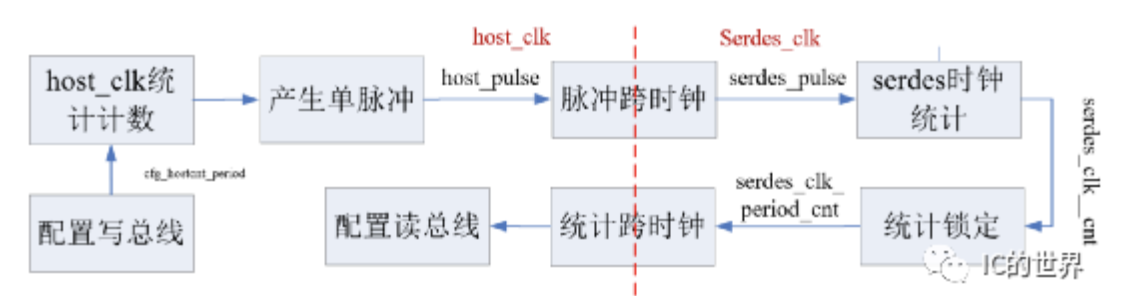

在芯片设计中,为了便于定位故障,有时候需要确认部分时钟频率是否正确,需要部分debug手段。常见的方式是:将时钟信号引到芯片管脚,通...