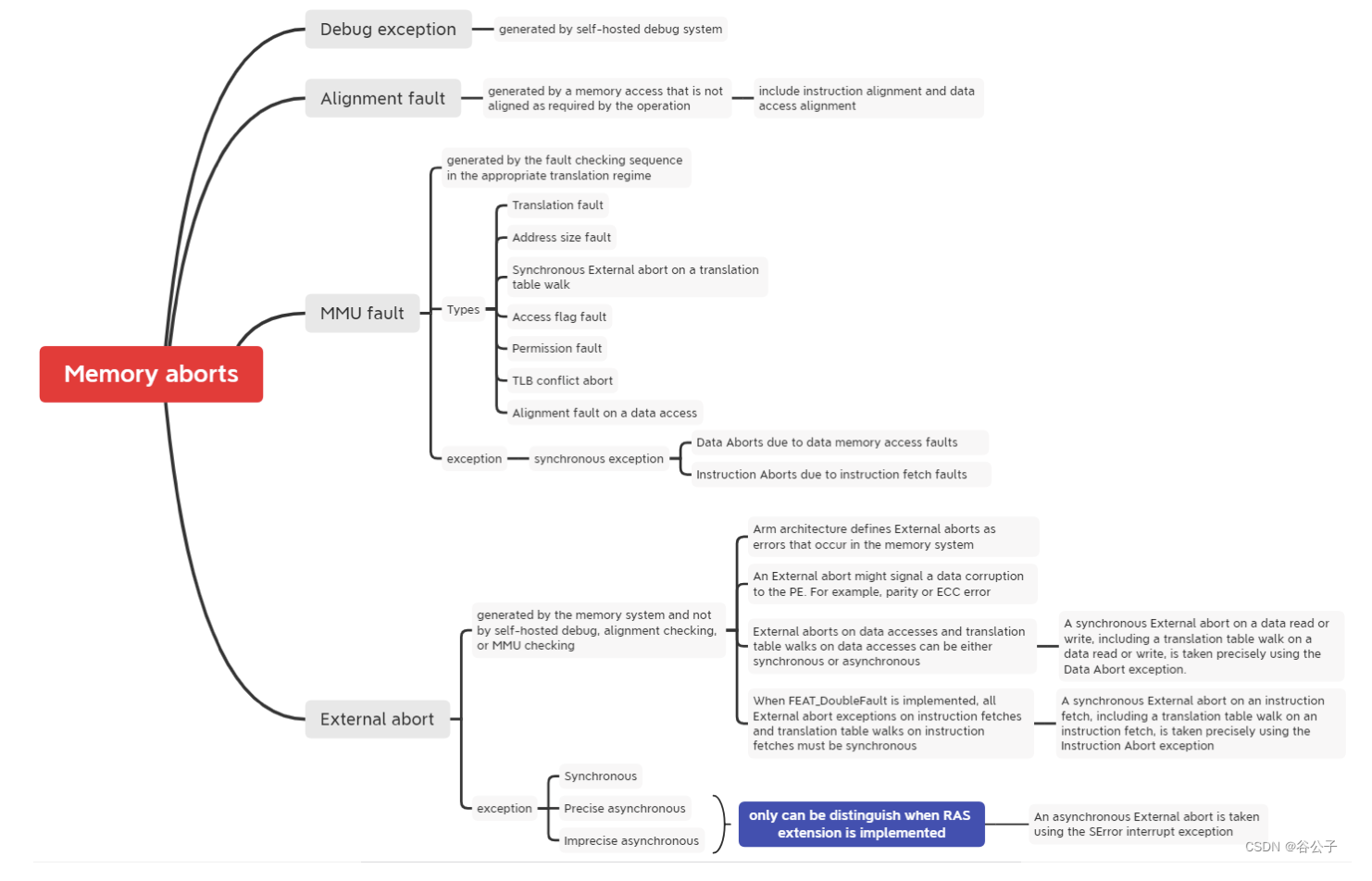

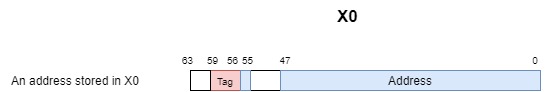

在AArch64 Virtual Memory System Architecture中,有以下几种机制会导致PE在访问memory失败时产生exceptions。

相信很多ICer们在Light芯片的过程中无论前后端都听过DFT设计测试,DFT全称Design for Test(即可靠性设计),众所周知,测试的目的是为了...

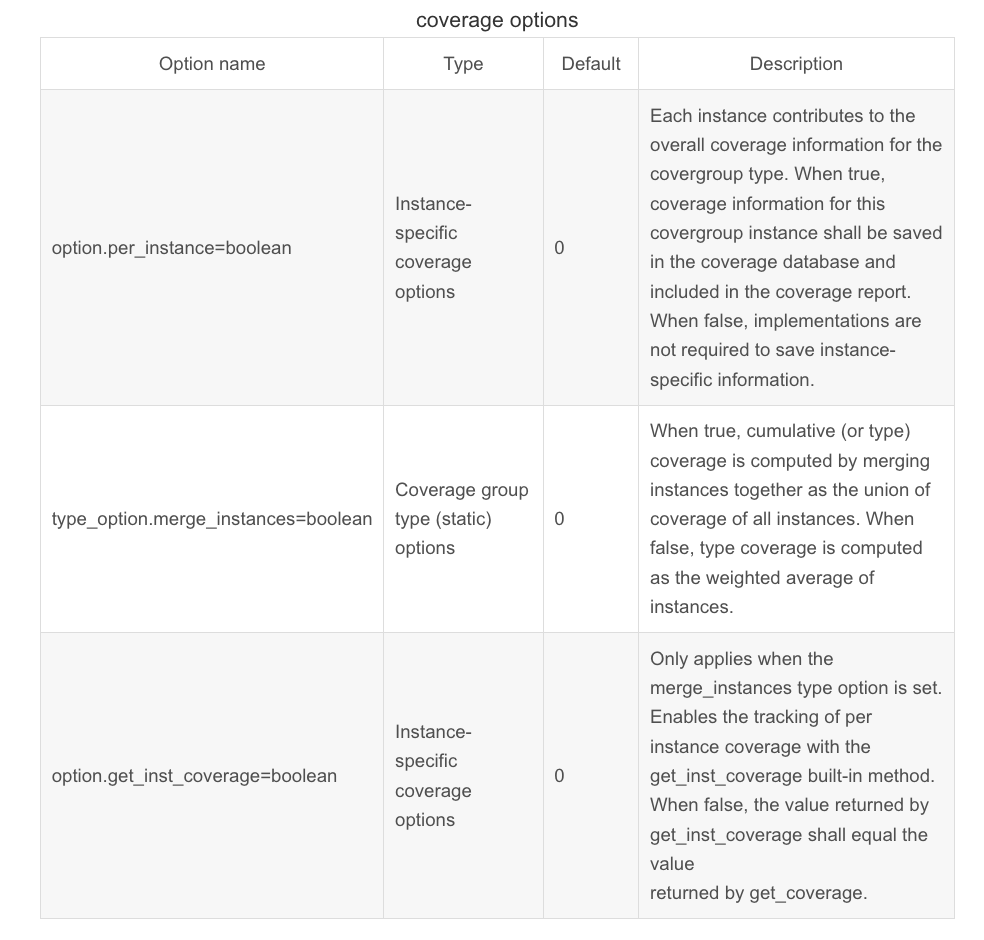

在systemverilog中,对于一个covergroup来说,可能会有多个instance,我们可能需要对这些instance覆盖率进行操作。

2023年1月18日,“逐梦芯时代,青春正当燃”第七届全国大学生集成电路创新创业大赛(“集创赛”)正式在线上召集同学们报名。

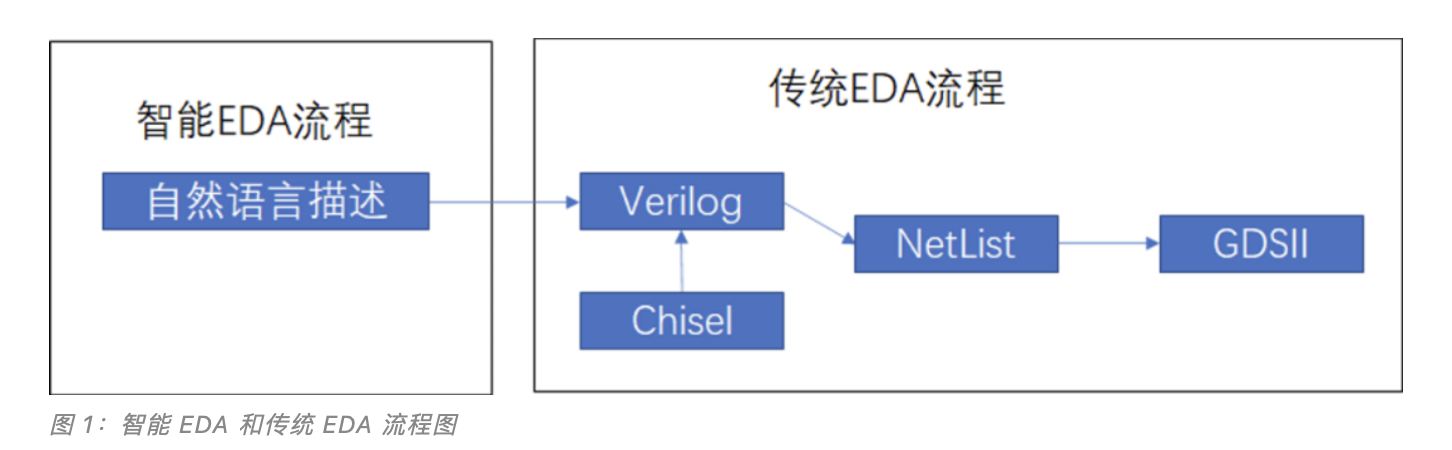

提到 ChatGPT,你会想到什么?提到芯片,你又会想到什么?可以把你脑海中浮现的第一个词记下来,看完这篇文章,肯定会改变你的看法。如...

MTE tag放在访问地址的bit 56:59,比如通过LDR Xm, [Xn]访问内存,Xn里面存放的是访问地址,当MTE使能的时候,真正用于访问内存的地址是...

集成电路 (IC) 设计是一项复杂的工作,不断突破密度和性能的界限。现在,人工智能 (AI)在 IC 设计中的作用越来越大。

《优秀的IC/FPGA开源项目》是新开的系列,旨在介绍单一项目,会比《优秀的 Verilog/FPGA开源项目》内容介绍更加详细,包括但不限于综合...

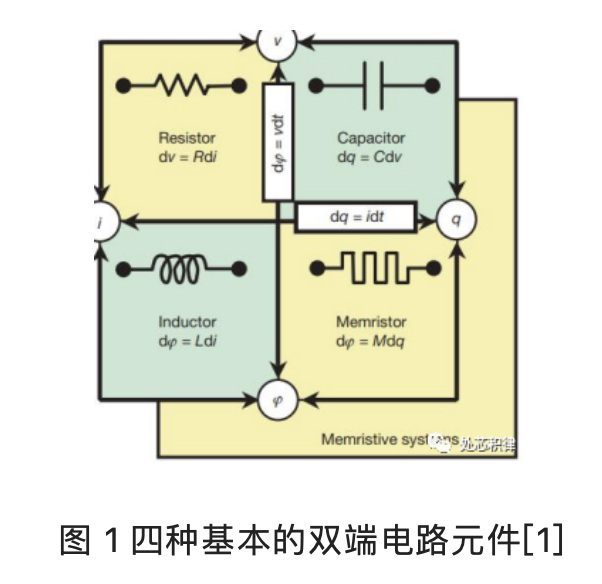

随着信息社会的发展,人类社会产生的信息总量开始呈爆炸式增长,这给数据传输、存 储、分析和安全带来了各种挑战。存算一体化技术被提出...

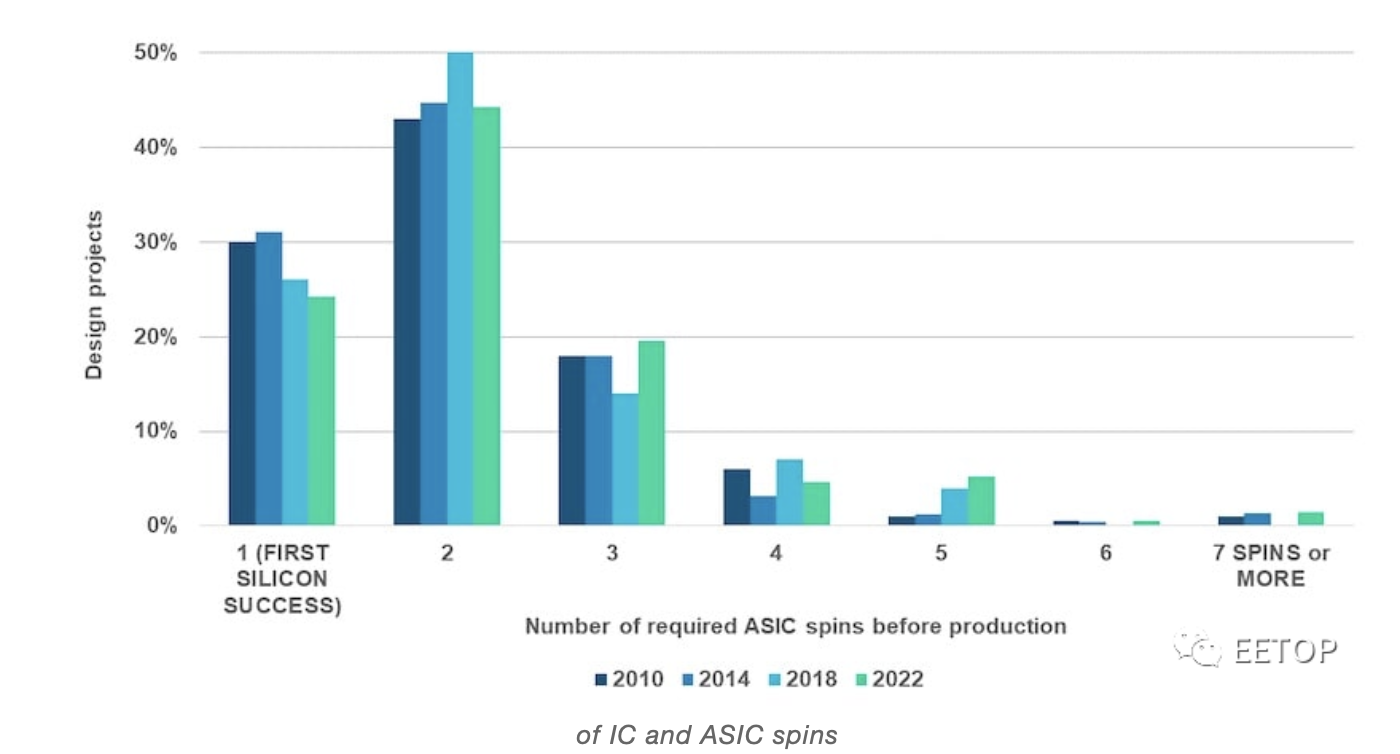

早在 2002 年,Collett International Research 就有一项关于功能验证的研究,自 2010 年以来,Wilson Research Group 继续进行此类研究...

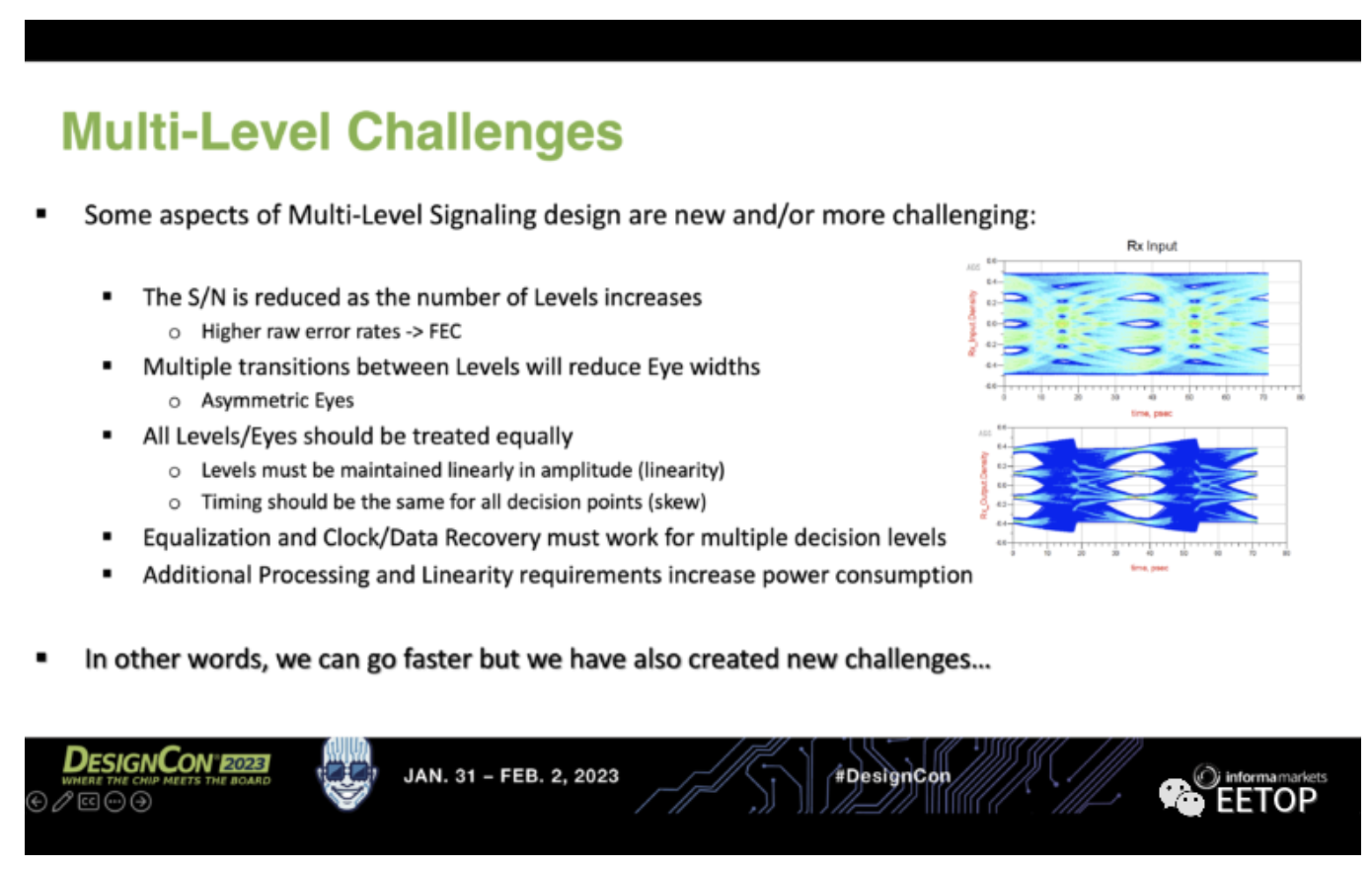

作为首屈一指的高速通信和系统设计会议,DesignCon 2023提供了来自各种专家对一些技术主题的深刻见解。在高速通信领域,多年来,PCIe在...

《芯片设计五部曲》:模拟IC、数字IC、算法仿真、存储芯片和总结篇芯片设计五部曲之一 | 声光魔法师——模拟IC芯片设计五部曲之二 | 图灵...

Ixana是一家专注于分布式计算的人机界面公司,最近开发了Wi-R,这是一种全新的通信协议,它将人体变成了一种可以传播信息的媒介。随着可...

最近在测试u8g2库,准备是在单片机上使用的,不过目前我看到其也是支持了linux设备的,所以想着是不是能在T507上跑下。搜了下已经是有人...

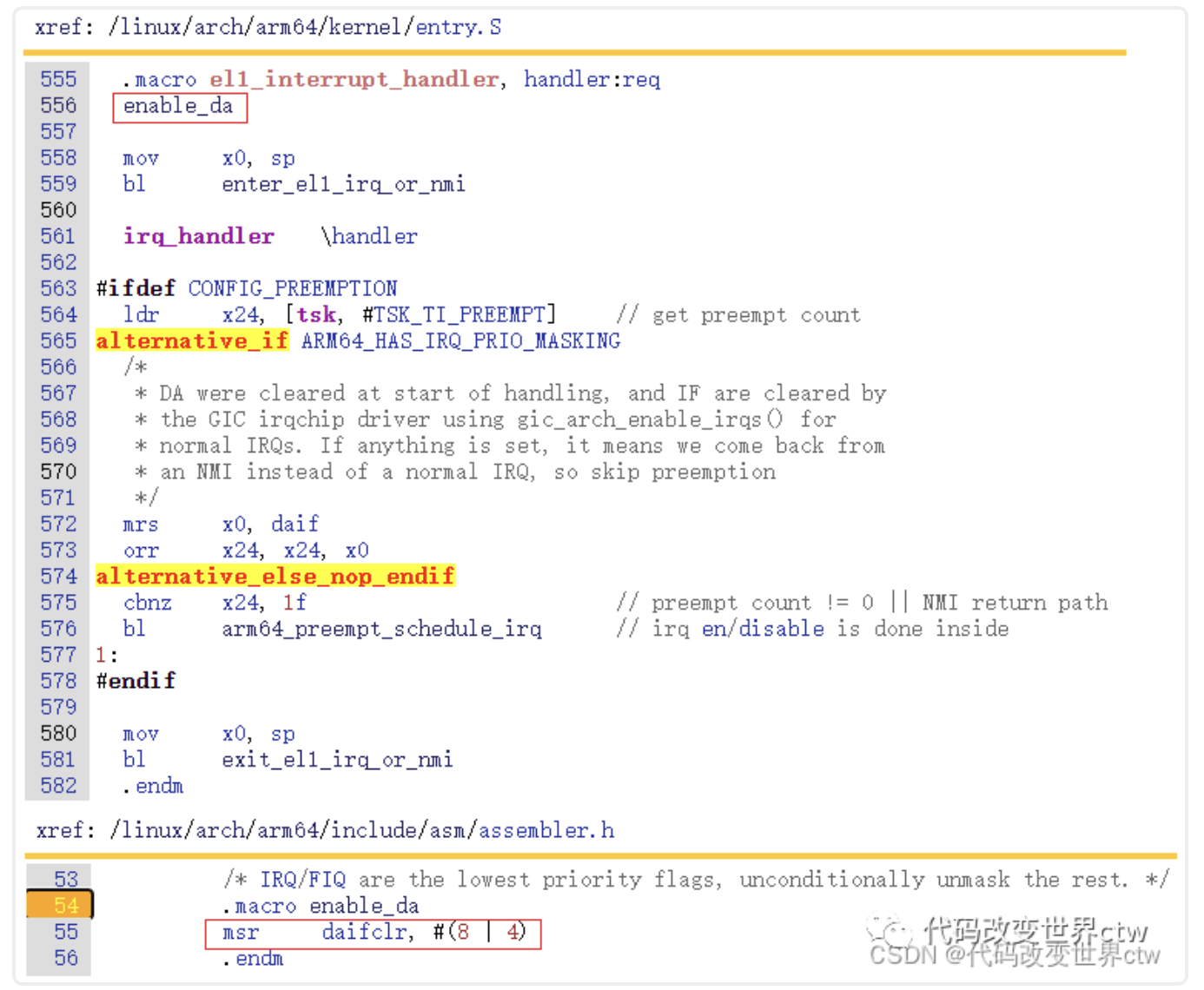

1、当一个irq/fiq正在执行时 ,是否可能会其它的irq/fiq打断呢?(1)如果开启了中断优先级,则在irq/fiq进入的时候,也会再次enalbe ir...

当然,有人会说,当年搜索引擎出现的时候也引起了人们的担心。还有,alphaGo当年也引起了不小的轰动,各路AI公司都一夜之间冒了出来。这...

串行数据传输与并行数据传输相比具有重要优势,在许多系统中,这些优势足以证明添加串行化和反串行化并行数据的电路是合理的,以便它可...

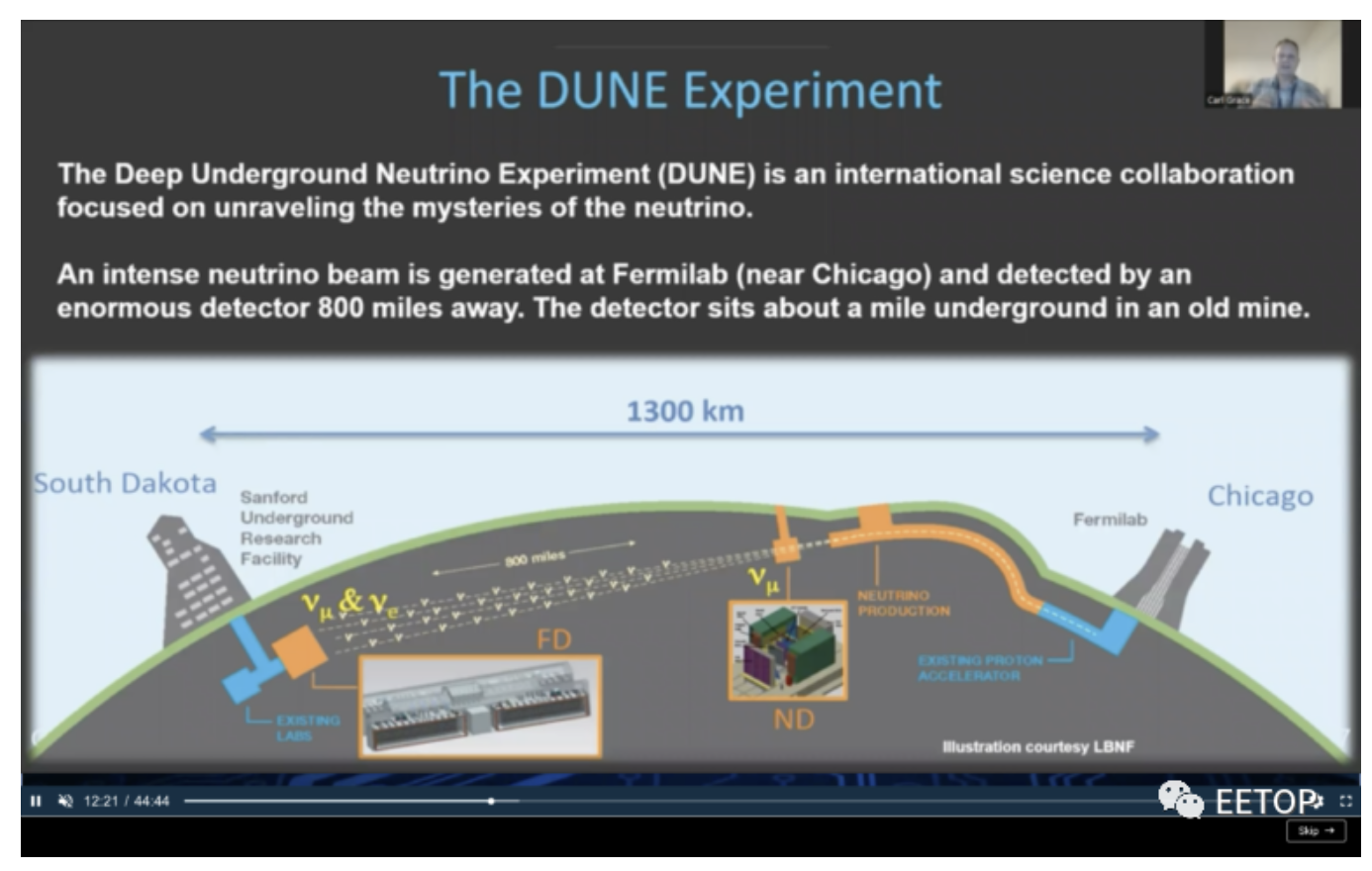

Cliosoft最近举办了一次网络研讨会,劳伦斯伯克利国家实验室(LBNL)的科学家Carl Grace谈到了一个检测中微子的尖端项目。该项目被称为...

技术改变生活。最近一段时间,OpenAI旗下的ChatGPT大火。根据官网自身的介绍(见图1),其是由 OpenAI 提出的大型预训练语言模型,使用...

我们有很好的CPU和传统GPU工作负载基准测试应用程序,但支持硬件光追(Hardware Ray Tracing)的新一代处理器呢?Basemark发布了全球首...