Mobileye、地平线、芯擎、寒武纪、芯驰、黑芝麻、杰发、宸芯这些汽车SoC芯片厂家背后都有Arteris的IP,除此之外,博世、NXP、意法半导体...

近日,电子发烧友网留意到,安谋科技在其官方微信公众号发表一封公开信,信中指出,公司新任联席首席执行官刘仁辰博士和陈恂博士已全面...

在碳达峰、碳中和进入全球化推进的时代,电子纸设备作为新兴的环保产品,凭借不伤眼、超低功耗等优异特性,已广泛应用于智慧办公教育、...

在音箱、电视、耳机、词典笔、智能屏、健身镜之外,小度于六一儿童节又发布了一款全新品类产品——小度语音智能闹钟 Pro。 新品发布会很有...

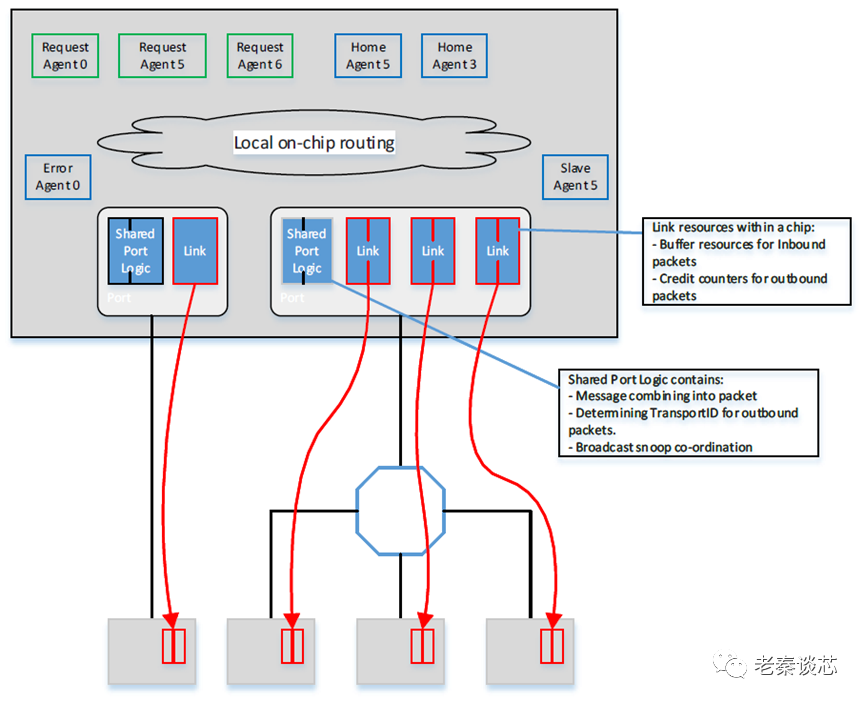

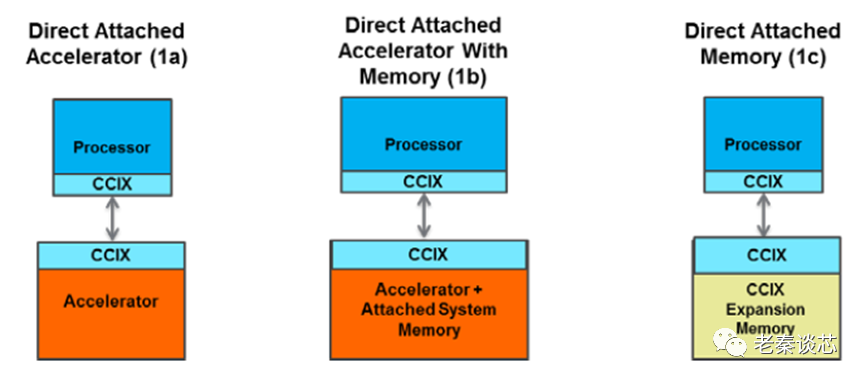

每个CCIX端口可以与一个或多个其他CCIX端口通信。CCIX交换机(Switch)包括CCIX端口并支持CCIX链路。CCIX链路定义为两个CCIX端口之间的...

✎ 编 者 按 在仿真里,信号的驱动究竟是在时钟沿之前还是在时钟沿之后?》关于仿真中信号驱动那点事儿 记得在SystemVerilog中,...

推荐一篇本团队近期发表的论文,一种用于智能网卡或DPU或可编程交换机的,支持P4语言的高性能开源解析器的设计。通信芯片也如CPU和DPU一...

正文开始前,闲扯几句。在接下来分析CCIX规范的过程中,大家会发现CCIX里面有太多ARM的影子,尤其是协议层的一致性协议部分,你会看到有...

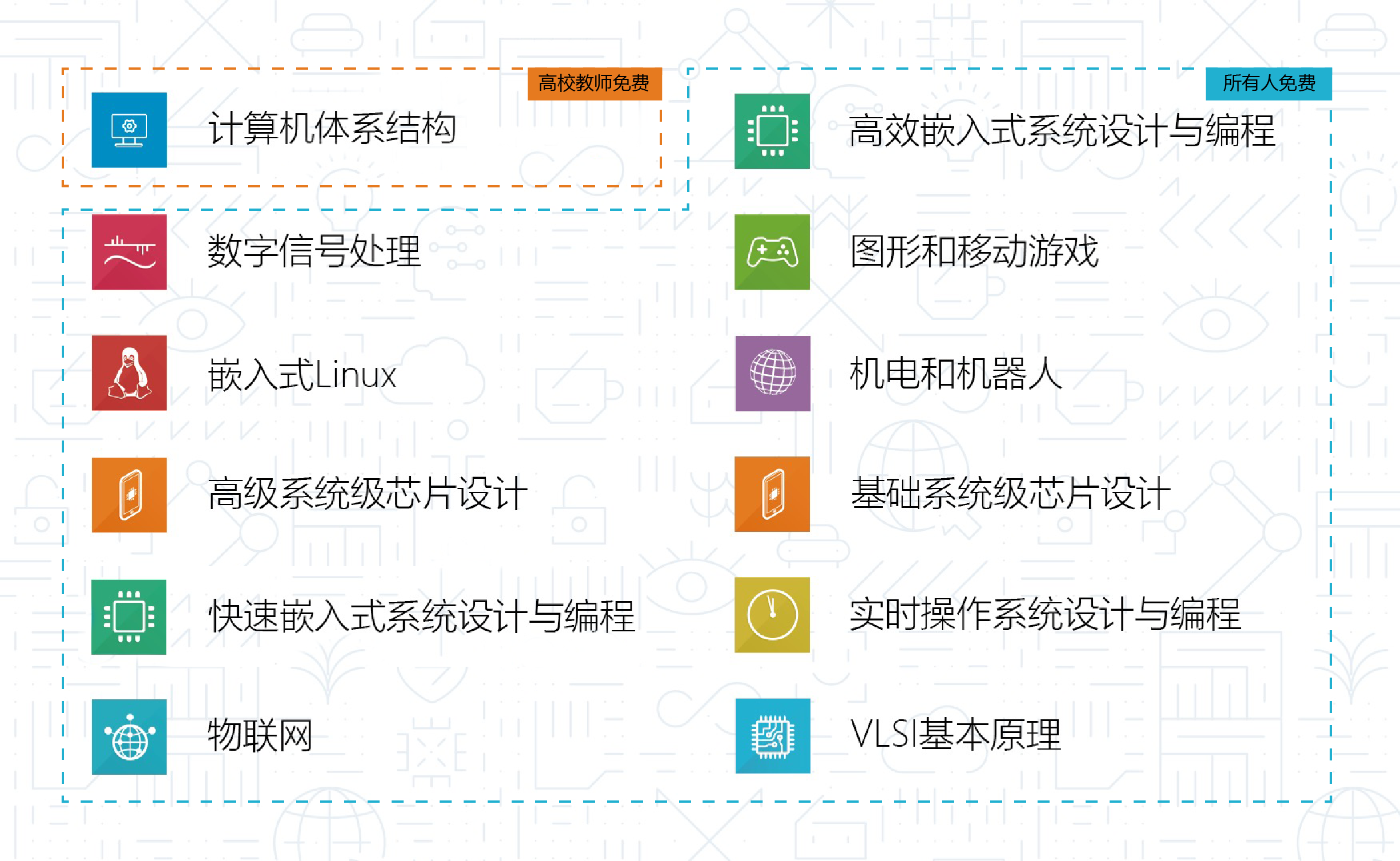

Arm教育计划开发了12种教育套件,其中的课件足够进行一个学期(10-12 周)的教学,包括PPT格式的课堂讲稿和带有解决方案的实验练习材料等。

Zynq SoC 监控自身电源电压和片上工作温度的能力是值得深讨的,我们可以在系统调试期间使用这种能力来验证初始电源电压和工作温度。然后...

5月23日,科大讯飞正式发布新款智能办公本Air,搭载瑞芯微RK3566新一代电子纸芯片。智能办公本Air轻薄便携,首次搭载AI摄像头,配备专业...

同时,也有同事看到我分享桌面时候操作 Snipaste 之后问我:“这是什么工具,看上去很好用的样子。”

PHY Interface For the PCI Express, SATA, and USB 3.1 Architectures

高通在上周五(5 月 20 日)的「骁龙之夜」主题活动上,更新了其 XR 领域最新进展,发布了搭载骁龙 XR2 平台的无线 AR 智能眼镜参考设计。

PHY Interface For the PCI Express, SATA, and USB 3.1 Architectures

PHY Interface For the PCI Express, SATA, and USB 3.1 Architectures

摘要:数据中心网络协议栈正在转向硬件,以在低延迟和低CPU利用率的情况下实现100 Gbps甚至更高的数据速率。但是,NIC中网络协议栈的硬...

刚上大学那年,去了趟宝马总部,他们信誓旦旦,要在2020年推出自动驾驶的产品。现在,各大车企稍微谨慎了些,宣称2025年能够让“相当比例...

PHY Interface For the PCI Express, SATA, and USB 3.1 Architectures

PHY Interface For the PCI Express, SATA, and USB 3.1 Architectures