本人专业电子信息工程,暑期在上海某外企做fpga相关的实习,9月开始投简历,主要找ASIC/FPGA 设计验证相关的岗。投了N家公司,挂了N个笔...

我们前面一篇仲裁器设计(二)-- Round Robin Arbiter里的Round Robin仲裁算法是一种公平的仲裁算法,每个requestor在得到许可之后优先...

里面提到了,固定优先级仲裁的一个问题就是公平性。以上篇文章里同学举手老师点名的例子来说,如果老师每次都叫学号小的,那学号大的同...

仲裁器Arbiter是数字设计中非常常见的模块,应用也非常广泛。定义就是当有两个或两个以上的模块需要占用同一个资源的时候,我们需要由仲...

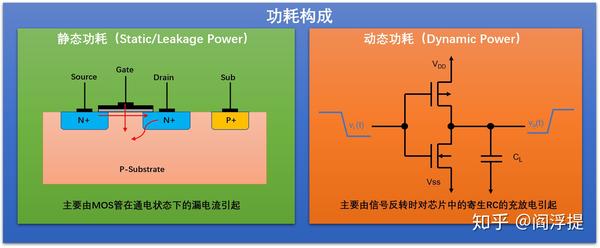

之前的文章我们引入了不少低功耗设计的基本概念,同时也介绍过芯片的总体功耗计算方法,其中就包括internal power的定义。今天想深入挖...

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为...

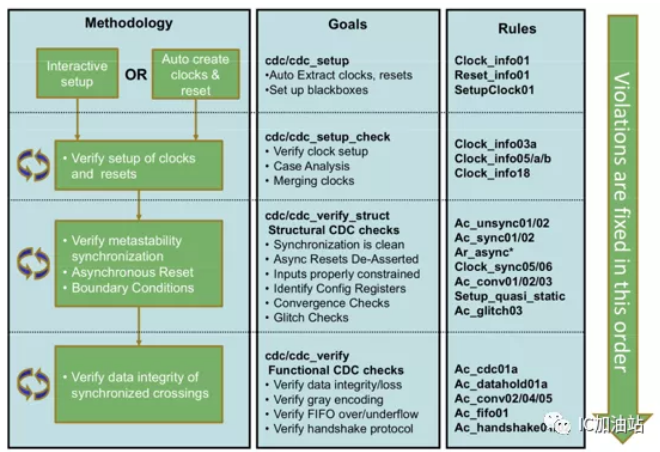

这一篇老李给大家简单介绍一下工业界常用的CDC检查工具Spyglass,然后奉上CDC设计和验证中的工程经验总结。如果你已经熟悉Spyglass CDC...

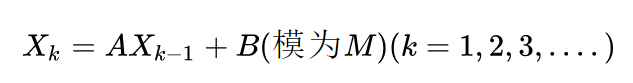

分频对于许多FPGA的学习者来说很常见,无论是偶数分频还是奇数分频。但是分数分频在我们制作时并不常见。现在我们来说分数分频。分数分...

作者:李虹江原文链接:[链接]面试必杀技:异步FIFO(下)-- CDC的那些事(6)本文结合了以上两篇文章,授权转自IC加油站微信号,未经作...

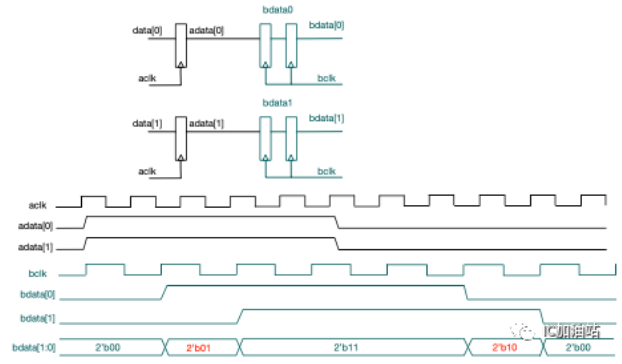

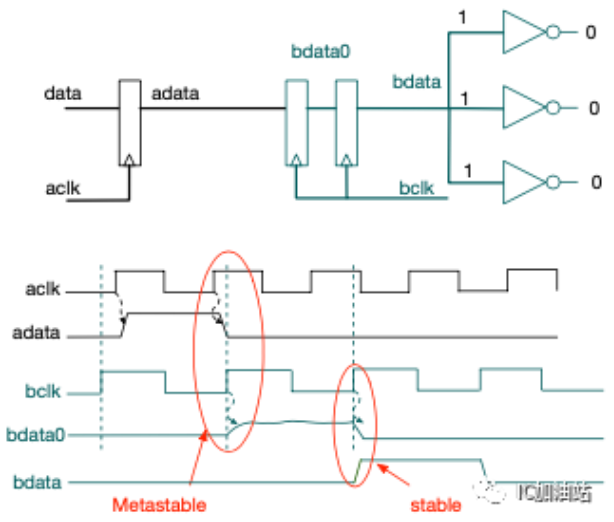

相信经过前面三篇CDC的那些事,大家对于单bit信号的跨时钟域有了相应了解(如果你还没有看,就先看看下面的链接)。下面老李带大家破解...

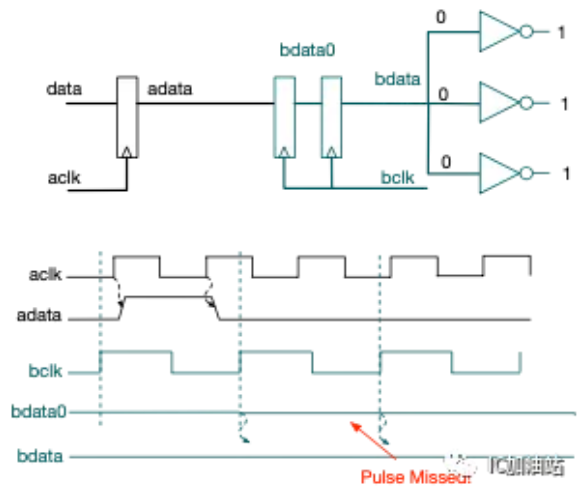

上一期老李挖了个坑,是关于同步一个时钟域的单周期脉冲(pulse)的问题。想当年这个问题老李在面试某几家大厂的时候被问到过不止一次,足...

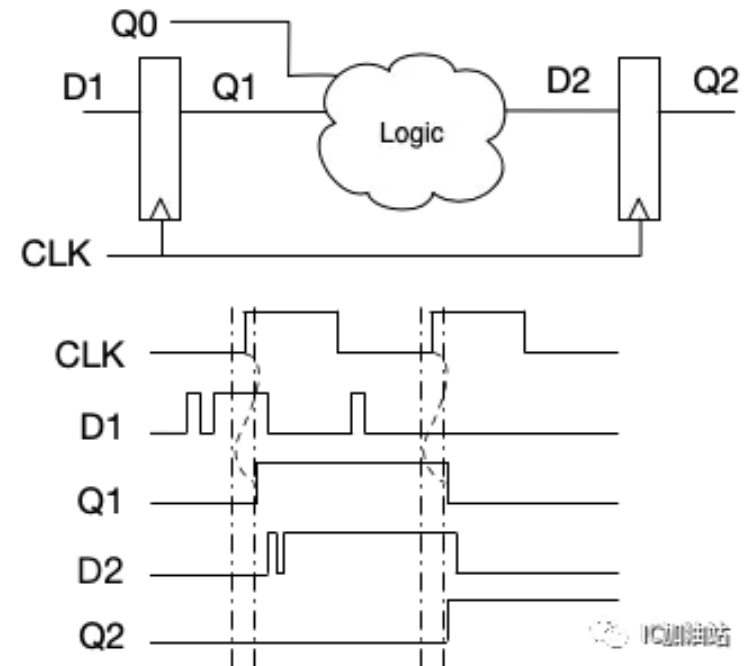

上一篇中我们回顾了一些基础知识,其中最重要的概念就是亚稳态。我们接下来所要看到的各种CDC的设计方法,本质上都是围绕在如何解决亚稳...

一转眼,老李在数字芯片设计领域又摸爬滚打了四年。上篇推送已经四年前了,久到我差点忘记了还开过这个公众号。前两天偶然想起,便觉得...

四十多年前,设计师从门级(gate-level)设计转向RTL设计,这种转变主要是由Verilog/VHDL RTL编码标准以及可用的RTL综合和实现工具支持...

本文章转载自:EDA物理设计技术作者:color is empty未经作者同意,请勿转载!随着摩尔定律持续演进,更高性能、低成本的电子产品利益了...

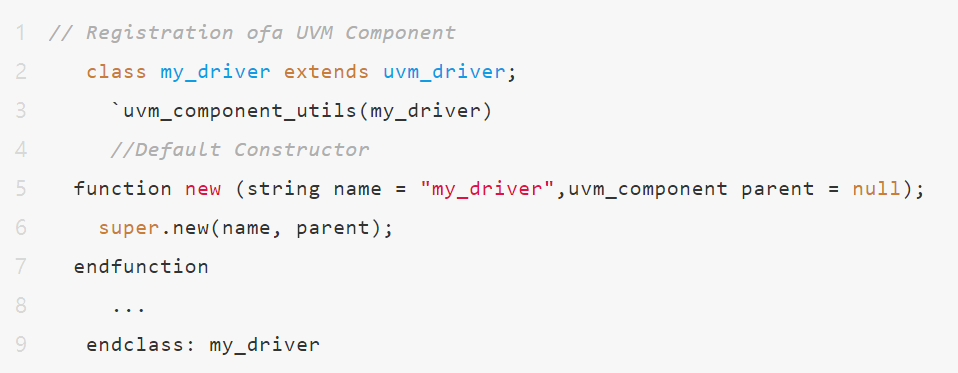

在文章数字IC验证系列之config\_db&virtual interface中我们已经简单地描述过factory设计模式或者说factory机制,在这篇文章中将阐述fac...

在我们之前的文章中,我们讲过了扰码器电路。在串行扰码器电路中,主要应用的就是线性反馈移位寄存器。今天我们就从伪随机序列的角度,...

随着现代医疗事业的蓬勃发展。医院病房监护系统和医疗会诊系统为现代医疗事业的发展做出突出贡献。主要的弊端就是病人身上的线缆,给病...

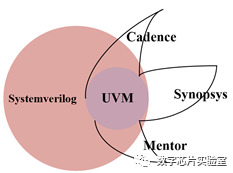

UVM提供了丰富的基类库和验证方法学,并且被主流的EDA工具、IP供应商和设计公司采用。现在,使用SystemVerilog基本上等同于使用UVM验证。

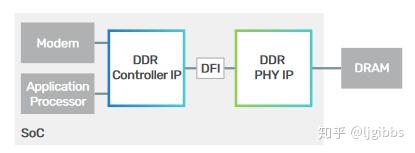

转载自:知乎DDR 是 SOC 的重要组成部分之一,随着 DDR 的速度不断提升,DDR 模块的设计难度也随之增大。目前 IC 设计公司一般从第三方...