从目前来看,EDA的主要创新并非算法创新,而是创新性的将现有算法应用于更多场景。可以说,EDA已进入到融合时代。

本文为《electronic design automation for ic implementation circuit design and process technology》中相关部分的阅读感想以及个人理解

和某大公司一位后端资深人士交流发现,其对于PVT中局部偏差,全局偏差概念似乎有些问题。正好本文进一步解释为什么说PVT corner仅处理全...

要了解ocv aocv socv pocv等概念,需要先了解与之相关的variation的概念,其实各种ocv其实就是对variation的数学抽象,区别仅是哪种更为...

因为需要前端工程师提供准确的vcd或者saif文件来进行switching activity的反标。

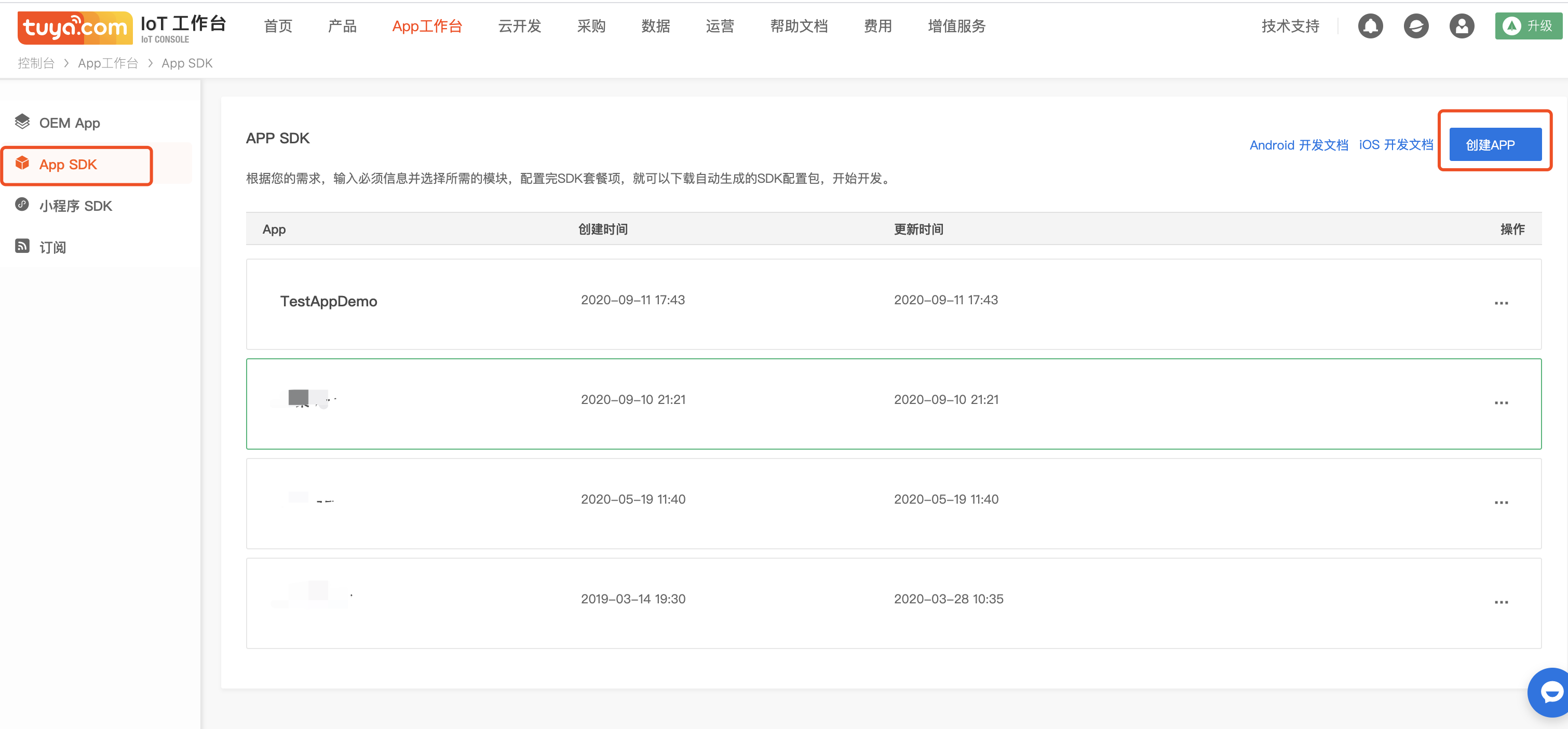

在如今物联网DCM(Device、Connect、Manage)的大框架下,有一个应用层来分析和处理数据,是必备技能。但是,对于一个公司来说,因为研...

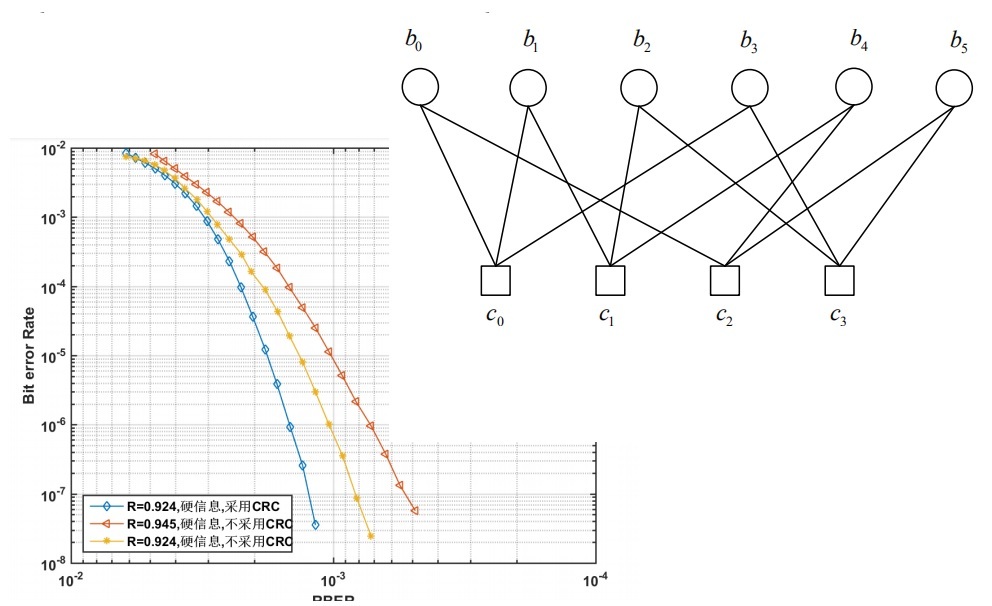

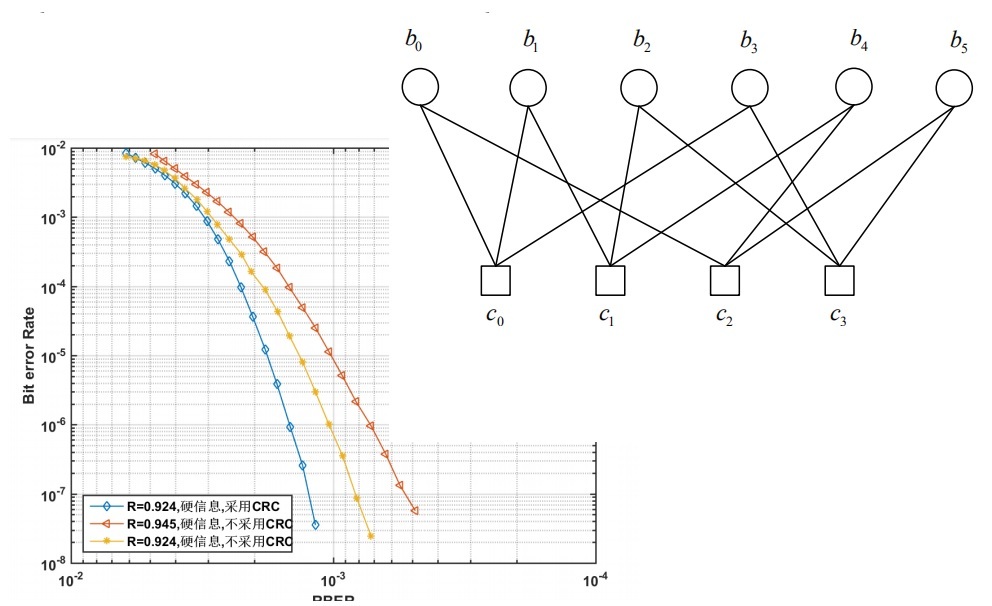

LDPC编码包括编码、RU算法编码、准循环码快速编码等算法。QC-LDPC码结构规律,便于硬件实现。我们根据上回书写到使用基于循环迭代消环的...

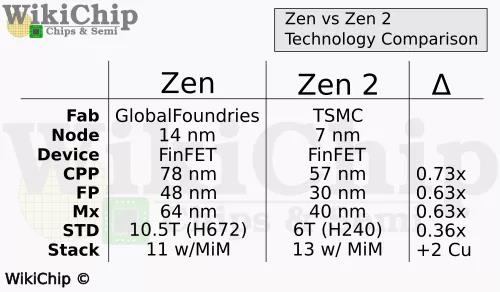

AMD Zen2,一个巨大 规模的巨无霸。采用的是先进的7nm工艺。而一个更矮的6T的标准单元库,导致的更高的逻辑密度和实现难度。相对于14nm...

我们经常会遇到这样的情况,block把timing修干净之后,交给做顶层的同事,结果会发现,仍然会有很多新的违例。

大多数情况下,我们timing signoff的标准电压的±10%范围内进行。而我们进行power signoff时,一般是要求电压降IR-drop为3%。今天我们就...

想了解就业市场最新动态?想查看目标岗位具体要求?想了解职业发展更好选择?那就关注“云上招聘”专栏吧!

检错码是能检测出数据传输中出现信息错误的一种编码。但是他要牺牲带宽,因为需要再在信息位后面附加检验信息来提供检错能力。我们最常...

leakage power在深亚微米下占比越来越高。在很多情况下,leakage power可能会占到芯片总功耗的30~50%。

微控制器自20世纪70年代诞生以来,经过了四十多年的发展,早已应用到了各行各业的产品中,各种各样的智能化产品也给人们的生产和生活带...

标准单元库的选择非常重要,选择一套适合的库,对于芯片时序收敛,物理收敛,以及最终芯片的PPA(performance Power Area)都非常重要。

power组成由dynamic power和leakage power组成。leakage power是指的电路在没有跳变时所产生的功耗。dynamic power则是指电路在跳变时产...

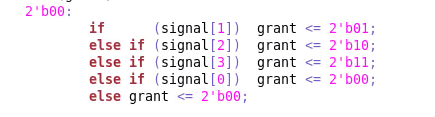

背景优先级仲裁器的关键缺点是,在非常繁忙的系统中,对于较低优先级的请求在收到授权之前需要等待的时间没有限制。另一方面,循环仲裁...

时序上很难满足的那些时序路径称为时序关键路径(timing critical paths),可以分为建立(setup)和保持(hold)时序关键路径。

想了解就业市场最新动态?想查看目标岗位具体要求?想了解职业发展更好选择?那就关注“云上招聘”专栏吧!

苹果在 11 月 11 日凌晨发布的 M1 芯片热度还没散去,11 月 12 日下午,三星在上海召开国内首场芯片发布会,发布了首款 5nm 移动芯片 Ex...