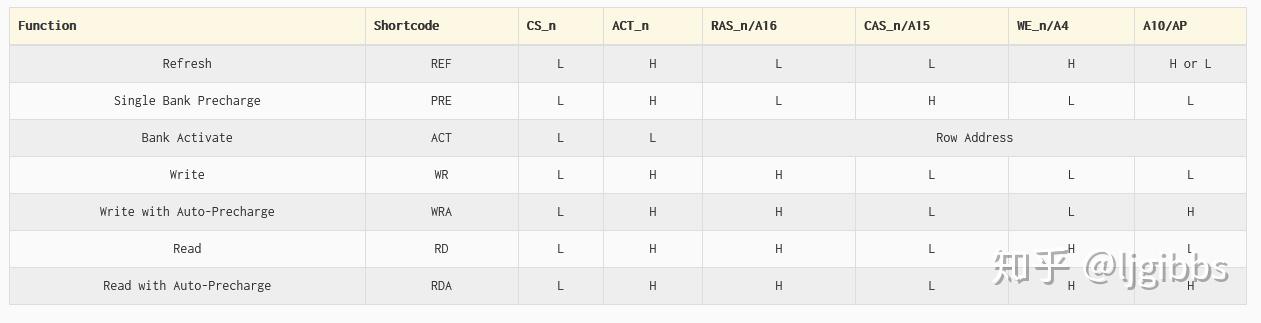

DDR4 的读写访问都基于 Burst 形式(译注:Burst 一般译作突发传输或者猝发传输)。突发传输起始时,由用户指定传输的起始地址,以及本...

文章首发于数字芯片实验室:[链接]Questa 仿真:具体代码:[链接]更多AMBA协议相关文章请关注极术专栏Arm AMBA 协议集。

加入openwifi项目,一起为openwifi添加更多更强大更有趣的feature!MIMO,WiFi6,WiFi7,雷达,无线安全 and more。

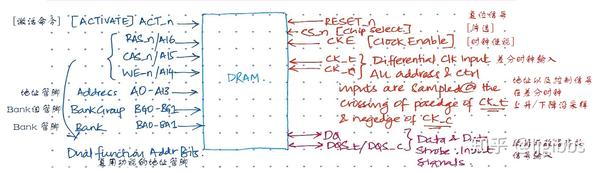

如今,DDR4 SDRAM 是基于 FPGA 或者 ASIC 的设备中非常流行的存储介质。本文我们将探寻 DDR4 的一些的基础知识:

这篇文章源自对知乎问题“博士生学历真的很重要吗?这个社会硕士,本科学历不就够用了。怎么还有那么多人想读博士?”的一个回答,看完心...

环境设置创建一个单独的目录(例如,innovus)。创建子目录synth和lib1、 将full\_adder\_pads\_syn.v移动到synth目录我们可以看出来这...

SystemVerilog在Verilog的基础上添加了许多新的数据类型,以提高仿真器运行时的内存利用率。

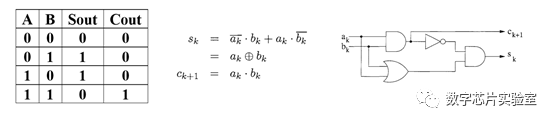

加减法是一类非常基础的运算,本文分析最简单的行波进位加/减法器(Ripple CarryAdder/Subtractor)的硬件开销和性能问题。

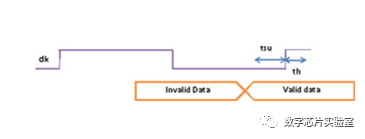

STA用于分析设计中的所有时序路径是否都时序收敛,其不需要输入激励。对于数字芯片设计工程师,必须要了解不同的时序路径和相关的STA概念。

我大学学的自动化,第一份工作是软件开发,windows桌面应用,用C和C++;第二份工作本来还是某为终端的软开,但因为个人原因入职推迟了三...

FPGA(现场可编程门阵列)也是一种IC。 顾名思义,只要有合适的工具和适当的专业基础,工程师就可以对FPGA进行重新编程。

仲裁器实现了两个CPU之间的仲裁算法(round-robin)。每个CPU都可以驱动请求输入信号(request[0] 或者request[1])。 仲裁器对请求进行...

将数据从一个时钟域传递到另一个时钟域类似于传递多个没有顺序关系的控制信号。但是不能使用同步器来同步数据信号,因为会采样到错误数...

将慢时钟域的控制信号同步到快时钟域通常不是问题,因为快时钟域将对慢时钟域的控制信号进行一次或多次采样。

纯粹的单时钟同步设计是一种奢望。大部分的ASIC设计都由多个异步时钟驱动,并且对数据信号和控制信号都需要特殊的处理,以确保设计的鲁...

9月10日,在商务部新闻发布会上,商务部发言人高峰称,今年1~8月,我国集成电路累计进口额达1.5万亿元,同比增长15.3%,高于我国外贸进...

1、define宏的使用:define经常用来代替某些复杂的文本内容或数字,也可以用来构造字符串。``

1、generate用法定义genvar,作为generate中的循环变量;generate语句中定义的for语句,必须要有begin,为后续增加标签做准备;begin必...

如果在设计初期,特别是作为新手第一次接触design compiler,急切地按下./run,自然会陷入虚妄:

1、Verdi中控制dump fsdb波形的一些系统task:$fsdbDumpvars - Dump the specified instances and nets.$fsdbDumpfile - Specify FSDB f...