在我工作中曾经帮助一些客户定位和解决芯片SoC硬件,CPU挂死问题这类疑难杂症。这类问题在被报告的时候,通常表现为软件不正常工作,例...

本文介绍了灵动 Mini-F5375-OB 开发板的参数资源、性能特点、主控、板载资源、原理图等信息,并完成开发环境搭建以及 Demo 例程测试

拿到Cix开发有一阵子了,写了一篇NPU的测评文章,链接在这:跳跳跳,发现大家好像对枯燥的技术性文章热情不高:

🧭 本文介绍了树莓派 RP2350 开发板结合 DHT11 模块、锂电池模块、随机眨眼动画,实现 OLED 显示的桌面动态温湿度计的项目设计。

这篇文章之前发过,当时主要是为 FPGA 的复位而写的文章,文章内的一些复位优缺点,对 IC 同样适用,考虑到这是面试常问的一个问题,所...

我们在编写一些比较复杂的 Verilog 代码时,通常需要进行大量的手动连线工作,这种工作十分容易出错,并且在代码模块的嵌套层级较多时,...

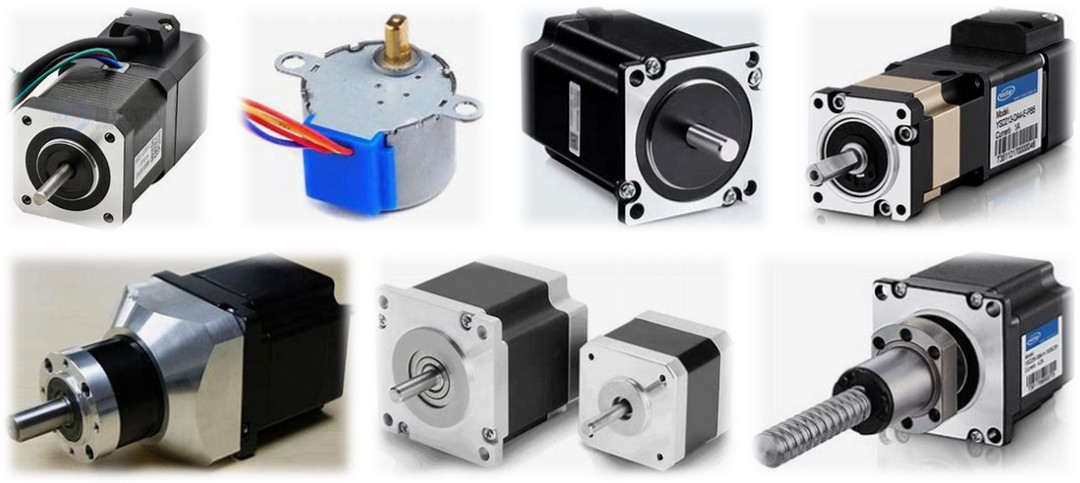

🧭 本文介绍了 DFRobot Beetle RP2350 开发板使用 LabVIEW 上位机串口发送指令,实现步进电机 单步 和 连续 旋转指定角度的项目设计。进...

🧭 本文介绍了 DFRobot Beetle RP2350 开发板实现步进电机驱动的项目设计,主要包括旋转角度的精确控制、串口发送实现自定义角度旋转、OL...

✎ 编 者 按最近因为工作原因在用 systemverilog 去写些东西,对于 systemverilog,一直缺乏一个在 IDEA 里写 SpinalHDL 的环境。在 VSco...

在 FPGA 的群里,经常会有人讨论以后 Verilog 会如何发展?HLS 和 DLS 谁会胜出?用 Python 来写更快还是现在用的相对多一些的 Chisel ...

X公司的发展蒸蒸向上,除了目前手上的项目,即将又有3个新项目上线,而且新项目架构复杂、规模大比原来项目大5倍以上,本就捉襟见肘的本...

1.循环循环的性能是由以下因素决定:循环内进行的工作;在循环中进行的检查,以确定它是否可以退出;在循环内进行的工作应该保持在最低...

Verilog 语言和 VHDL 语言是两种不同的硬件描述语言,但并非所有人都同时精通两种语言,所以在某些时候,需要把 Verilog 代码转换为 VHD...

从项目开始规划架构,并尽可能利用 IP 核来减少所需的开发量(并不特指官方 IP)。在层次结构方面,有几点注意事项:

PCIe 5.0服务器平台在2023年进入市场,到目前已经演进了两代,正逐步成为主流。Solidigm在推出PCIe 5.0 SSD的进度上相对竞品有所落后,...

【Mini-F5265-OB开发板试用测评】按键控制测试本文介绍了如何使用按键控制 MCU 引脚的输出电平。原理由原理图可知板载用户按键 K1 和 K2...

在构建复杂的 sequence 序列的时候,我们经常会用到 m_sequencer 和 p_sequencer,并且在很多资料中都提到两者实际指向的是同一个对象,...

传统观点认为,固态硬盘SSD总有一天会取代所有硬盘,但实际上,事实证明,固态硬盘对DRAM市场来说比对硬盘市场更具挑战性。

在搭建验证环境时,经常需要在环境中插入很多info用于输出一定的log信息用于进行debug,在插入这些info方法的时候,经常需要同时输出该...

低功耗和高速度带来了设计复杂性的增加。DDR5与前几代最显著的区别是引入了决策反馈均衡,这是一种用于串行链路系统来提高接收信号完整...

GIT batch是window下原生的GIT命令行终端,兼顾了GIT的命令特性,同时也支持很多UNIX的原生的bash交互方法。但是由于编码问题,在使用GI...

在Verilog中,文件读取和写入是非常有用的。从文件中读取测试激励输入,并写入输出以供比对。 在Verilog中读取或写入文件的方法很少。如...

DFT指的是Design for Test,而DV指的是Design Verification。这两种工作都同样具有挑战性,都是芯片设计流程中的关键步骤。

调试指的是在遇到工程问题的时候,通过一些手段来进一步诊断问题原因,探索解决方法,最终使得系统功能正常运行的必要过程。

写过Verilog和systemverilog的人肯定都用过系统自定义的函数$display,这是预定好的,可以直接调用的功能。但是当Verilog中的task和func...

如图2所示,复位跨时钟模块本质上由2到3个级联的异步寄存器组成,i_src_rst_n接到所有寄存器的复位端口,首个寄存器的D端接1,最后一个...

fork-join_none相信大家应该熟悉了,新来的朋友可以回顾下jerry之前的文章,就是之前jerry提到的那个“暴脾气”的哥们,他不会去等别人,...

AI技术在消费电子终端设备中的应用加速落地,推动了行业从弱复苏向成长的转变。消费电子行业处于快速迭代的发展阶段,不断涌现出新产品...

SystemVerilog是一种硬件描述和验证语言,用于描述电子电路的行为和结构。它建立在Verilog的基础上,具有几个附加功能。SystemVerilog标...

说明:这种方法相当简单朴素,python做出需要的字符串,写到文件。好处是不需要技巧,坏处是python代码可维护性较差。