软件定时器是用程序模拟出来的定时器,可以由一个硬件定时器模拟出成千上万个软件定时器,这样程序在需要使用较多定时器的时候就不会受...

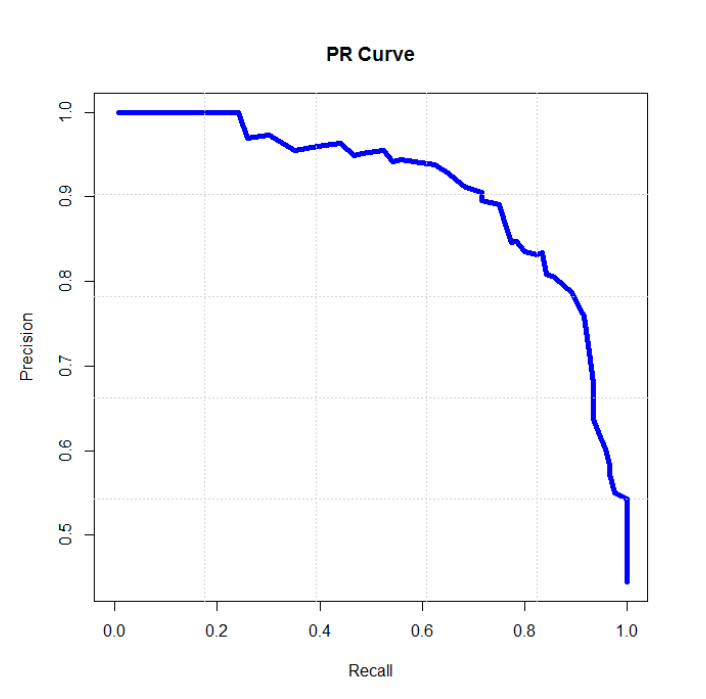

数据挖掘实践(金融风控):金融风控之贷款违约预测挑战赛(下篇)[xgboots/lightgbm/Catboost等模型]--模型融合:stacking、blending相...

“中国智能网联汽车产业创新联盟”是由工信部指导,中国汽车工程学会、中国汽车工业协会支持,既支撑政府决策、又服务行业发展的创新机构...

广泛的工作负载的性能,包括许多基准,如SPEC,依赖于基本数学例程的有效实现。这些例程可以通过矢量化和有效利用SIMD管线来提高性能。

内容生产,特别是创意工作,一向被认为是人类的专属和智能的体现。牛津大学计算机学院院长迈克尔·伍尔德里奇 2019 年写作的《人工智能全...

当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。而多片FPGA系统的一个最重要的痛点就是...

...

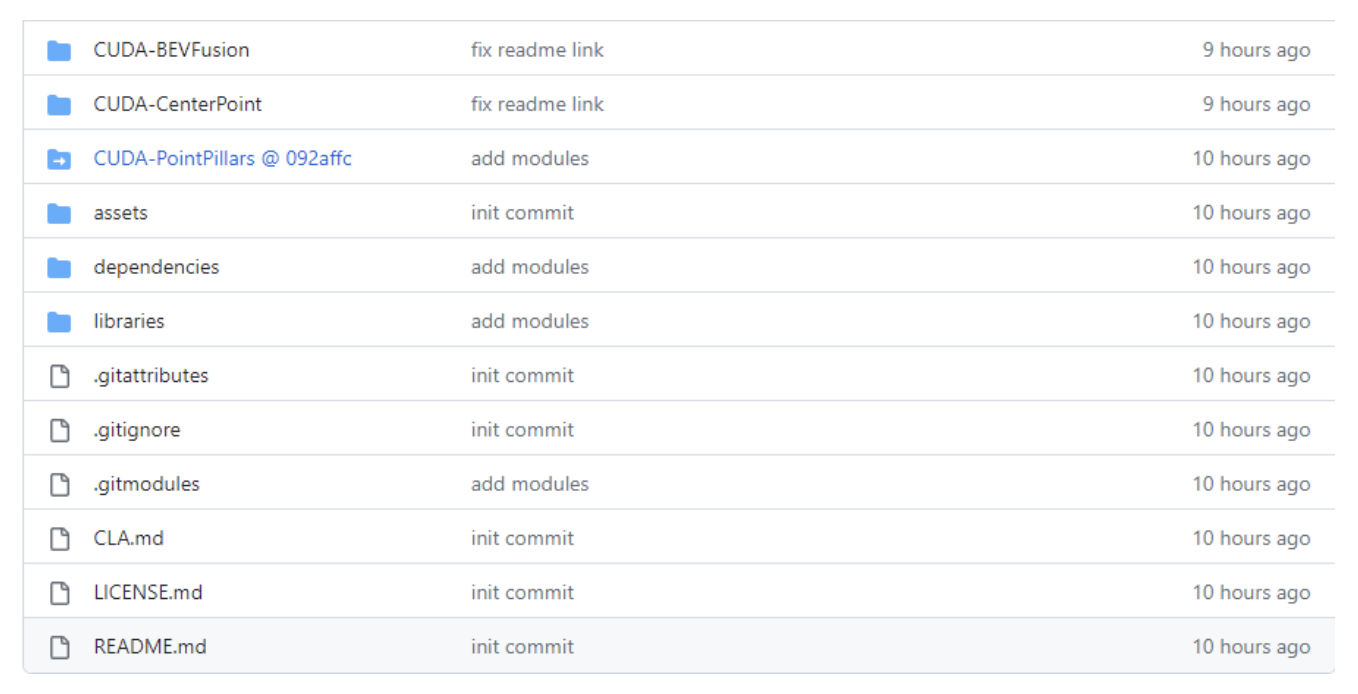

众所周知,雷达与相机的融合方案由于稀疏卷积的原因导致一直难以落地推广。而没有使用稀疏卷积的方案精度通常会差10-30%左右,并且目前...

我们最近和一些资深的汽车电子工程师一起,对汽车上各种各样的汽车电子部件进行深度解剖和分析。负责这个实验室的大神,是我们的汽车馆主。

本期,让我们一起走近i.MX9352处理器,深入了解这位i.MX系列新成员的GPIO该如何操作,以及它与前辈i.MX6ULL处理器又有哪些异同。

我们的首期直播将深度解读Armv8/Armv9内存属性,带你领略ARM架构的魅力。特邀嘉宾:Baron更多关于Baron的信息,请访问他的博客:[链接]...

我们习以为常的科技世界,正在以肉眼可见的速度被大模型所改变甚至重构。不想错失机遇的科技企业,都怀揣着造AI重器的梦想,各种大模型...

如果从1994年中国实行税制改革,要求以“以计算机网络为依托”开展企业税务工作算起,转瞬间,中国企业的信息化、数字化建设已经走过了近...

随着文娱活动的复苏,大量黄牛“卷土袭来”。顶象防御云业务安全情报中心发现,五月天即将开启内地巡演,北京鸟巢演唱会、深圳演唱会陆续...

安谋科技2023年实习生招聘开始啦,欢迎投递哦~期待您的投递!

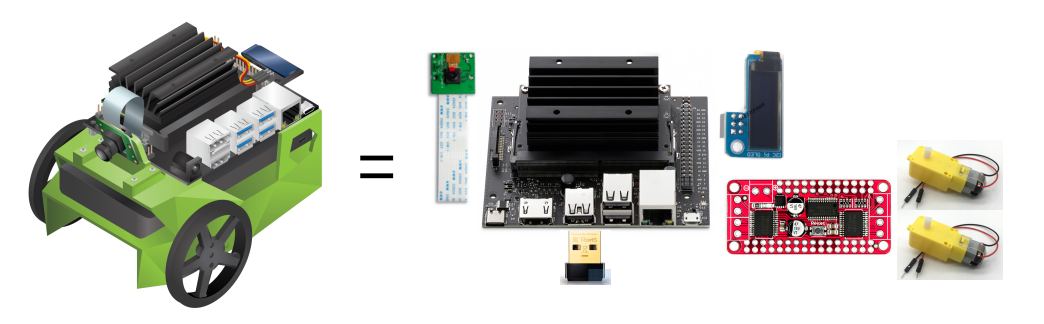

笔者从 2019 年开始使用 NVIDIA Jetson Nano 开发套件,一开始是被 NVIDIA 当时推出的 Jetbot 智能小车所吸引,这套 2,000 元以内能实现...

近日,安谋科技(中国)有限公司(以下简称“安谋科技”)获得ISO 26262:2018 ASIL D级别以及 IEC 61508:2010 SIL 3级别功能安全流程认...

如果说20年前最热的软硬件组合是Windows+ X86的话,那么今天最热的组合便是LINUX+ ARM。对于从事技术工作的广大程序员来说,今天正是学...

AI大模型已经在AIGC领域展现出了前所未有的创造力,它被认为是人工智能突破“认知智能”的有效路径,并正在作为算法基础设施革新各行业的A...

提起清代赵翼的名字你或许很陌生,但是上面这句诗却是脍炙人口,也给人一种风云变幻、桑海桑田的使命感。在如今这个“百年未有之大变局”...

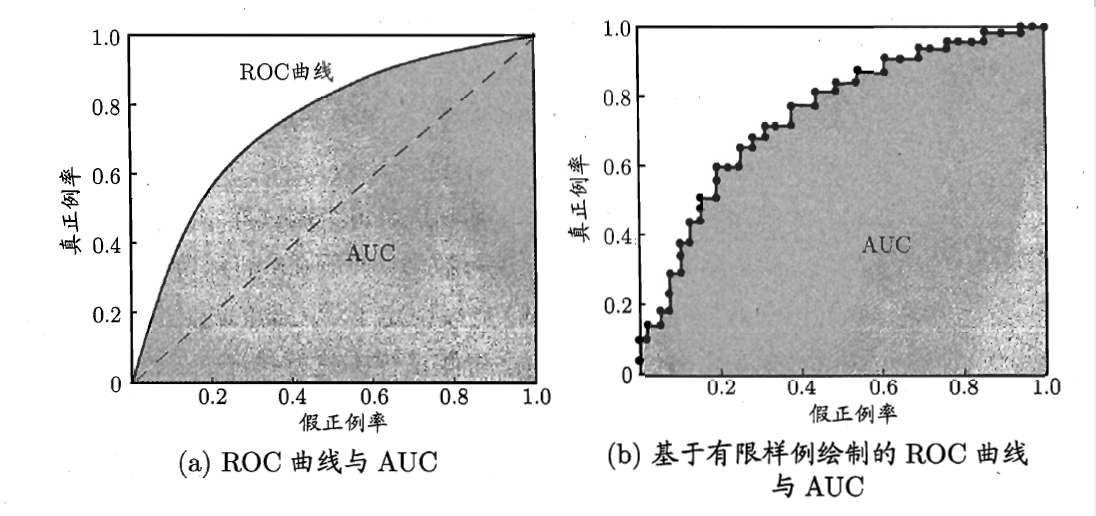

赛题以金融风控中的个人信贷为背景,要求选手根据贷款申请人的数据信息预测其是否有违约的可能,以此判断是否通过此项贷款,这是一个典...

GitHub Copilot 是一款由 GitHub 和 OpenAI 共同开发的人工智能编程助手。它是一种基于机器学习的代码自动完成工具,旨在帮助开发人员更...

Bing Chat 是微软推出的一款全新的搜索体验,它不仅可以提供传统的网页搜索结果,还可以和用户进行智能对话,回答问题,提供建议,甚至...

集微网报道 (文/陈兴华)鉴于在金融投资界的强大影响力,巴菲特清空台积电股份的消息一时甚嚣尘上,部分舆论甚至为台积电“哀嚎”。但殊...

2023年5月11日,Google I/O年度开发者大会完美落幕。随着PaLM2模型发布、Bard的自由访问,技术彻底迎来了“AI 时代”。

Title: X-Decoder: Generalized Decoding for Pixel, Image and Language Paper: [链接] Code: [链接] Demo: [链接]

新闻背景:5月15日,著名经济学家任泽平在社交媒体发文,建议推出五年内燃油车禁售时间表,河北以南,大力发展新能源,双碳,扩大内需。

美国的主要汽车制造商,包括福特、通用和特斯拉,以及新兴力量Rivian和Lucid,都在2023年第一季度发布了他们的业绩报告,揭示了他们在中...

上周刚刚结束的「飞凌嵌入式系列讲座-第1期」直播得到了大量的关注,数千名工程师小伙伴共聚直播间一同学习关于多核异构处理器双核通信...

FPGA设计的五个主要任务:逻辑综合、门级映射、整体功能逻辑布局、逻辑资源互连布线,最后生成FPGA的bit流,根据常用的FPGA工具...