AMBA总线是ARM研发的(Advanced Microcontroller Bus Architecture)提供的一种特殊的机制,可以将RISC处理器集成在其他IP芯核和外设中...

前言之前有记录过关于总线的概览学习:【FPGA验证学习(五):SoC的总线架构】[1]【SoC系统结构设计(三):SoC中常用的总线】[2]【关于...

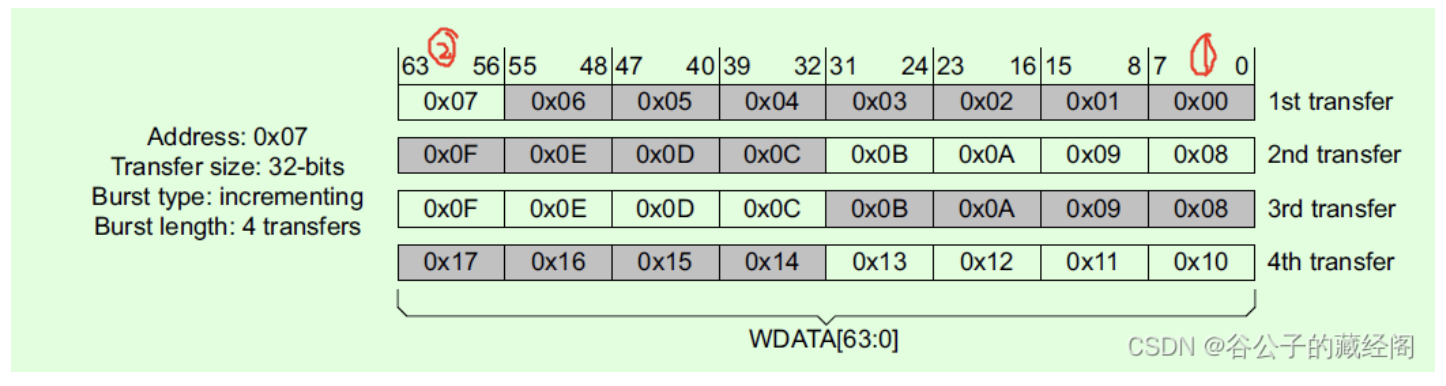

前几天帮一位同事分析了下write data在AXI write data channel上排布,想想还是记录一下,方便日后复习。我们先来看一张wdata排布图,灰...

提纲:1. AXI基本概念AMBA总线中APB,AHB,AXI的关系读操作写操作2. AXI OrderingOutstanding。Aw-W-B的valid/ready依赖关系AR-R的valid/...

使用 AMD-Xilinx FPGA设计一个全连接DNN核心现在比较容易(Vitis AI),但是利用这个核心在 DNN 计算中使用它是另一回事。本项目主要是...

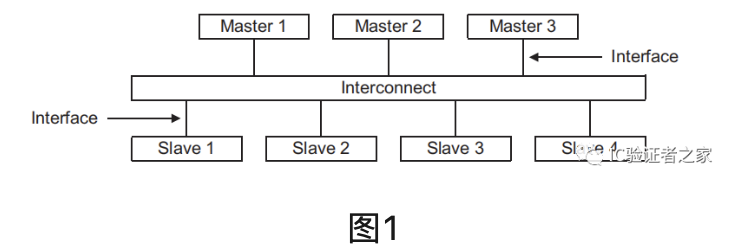

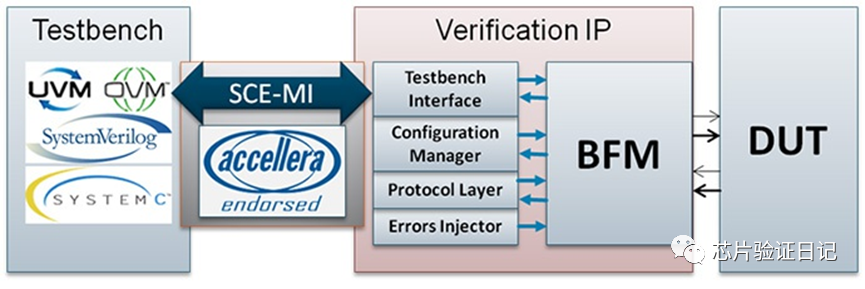

当今的SoC芯片,普遍包含大量的工业标准接口同外围设备相连。 在验证设计过程中,这些接口被用于和测试testbench相连接。这些沟通桥梁,...

AXI总线在FPGA设计中使用越来越频繁,但初学的同学经常会因为对协议的理解不够深入,写出来的代码经常会出现死锁等问题,对FPGA设计与调...

用户空间支持当CONFIG_ARM64_MTE使能而且CPU硬件也支持MTE时,Linux通过HWCAP2_MTE属性告诉Usersapce kernel支持MTE功能。

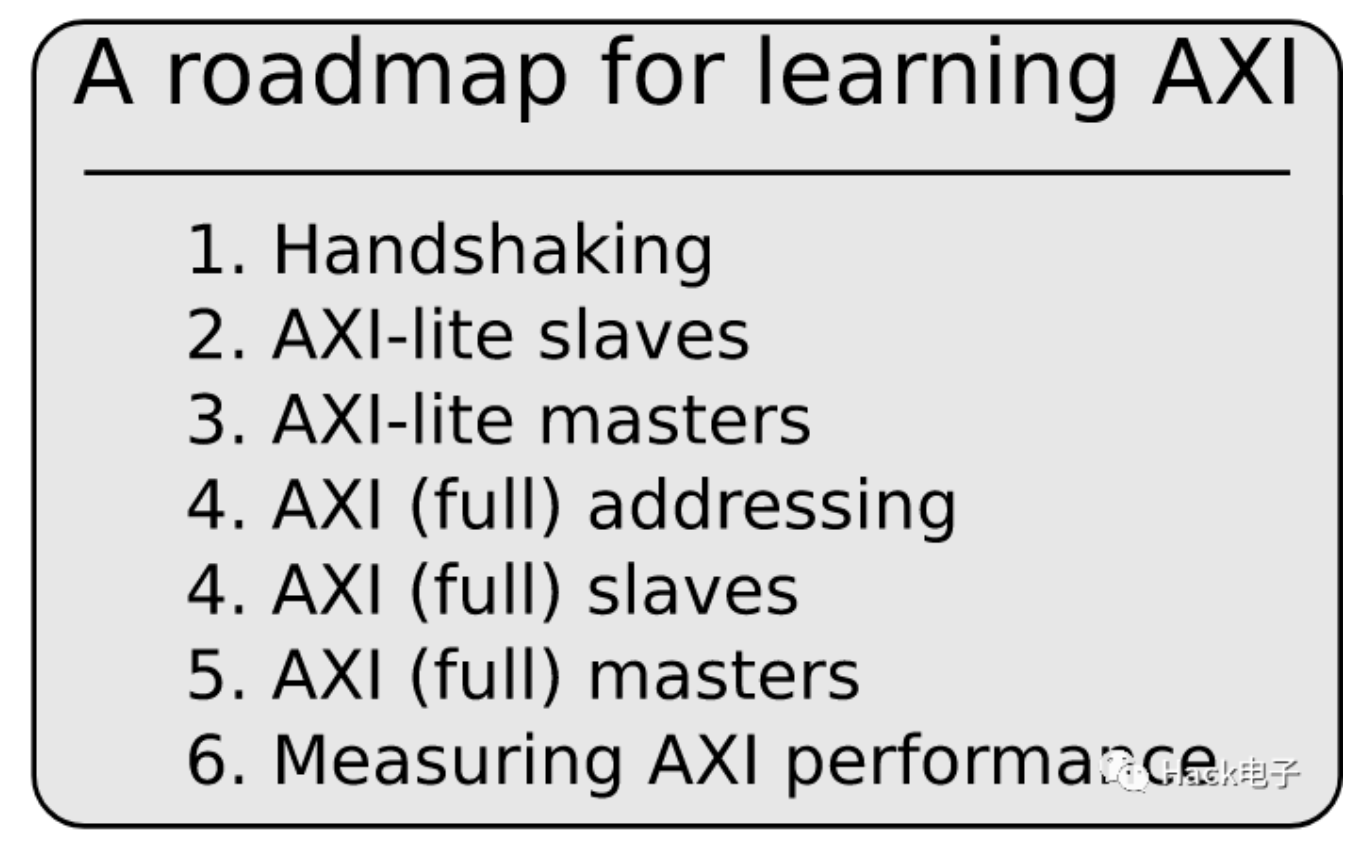

曾经有人在 Reddit 上问,应该如何学习 AXI 协议?ZiPCUP(学习网站链接)上的大佬针对此问题总结了自己的学习路线,尤其针对一些网上的...

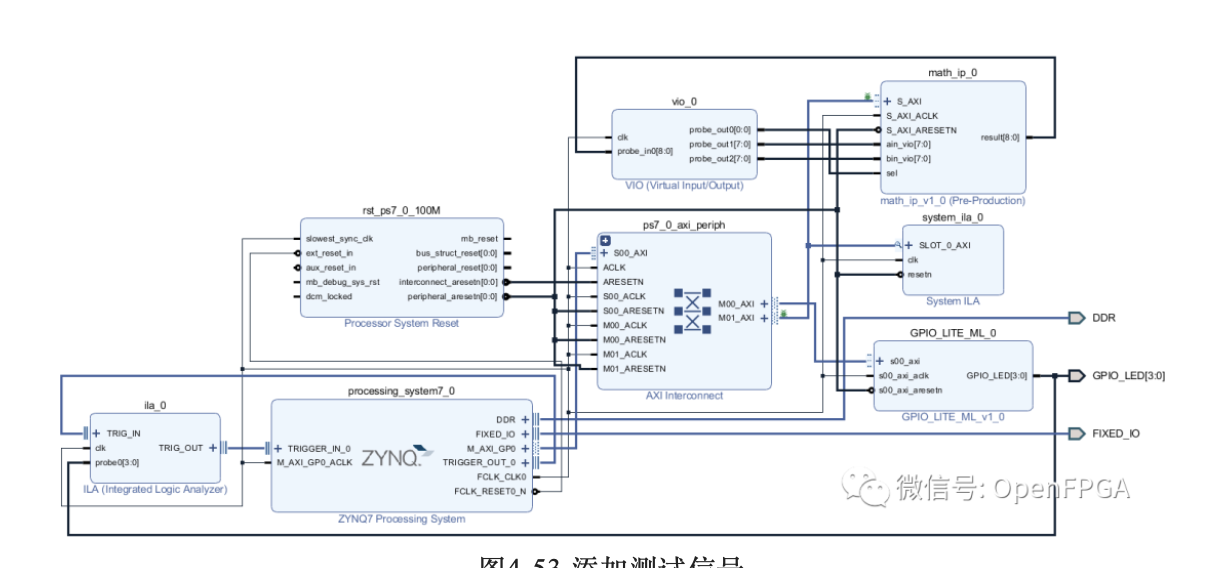

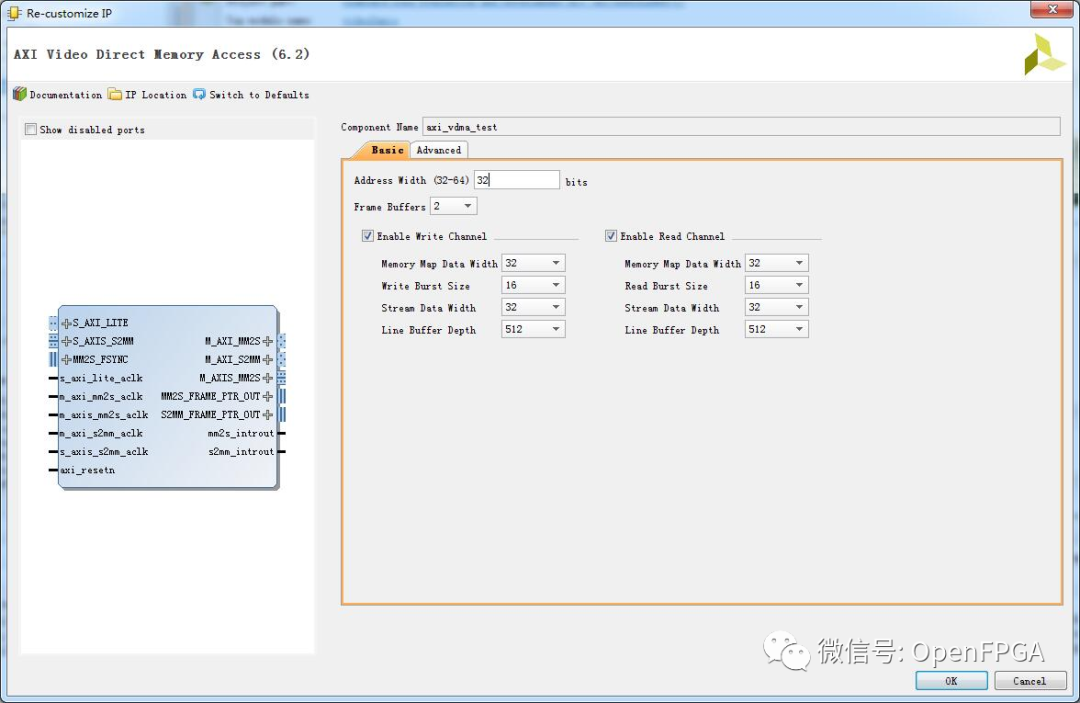

在《AXI-Lite 自定义IP》章节基础上,添加ila\vio等调试ip,完成后的BD如下图:图4‑53添加测试信号加载到SDK,并且在Vivado中连接到开发...

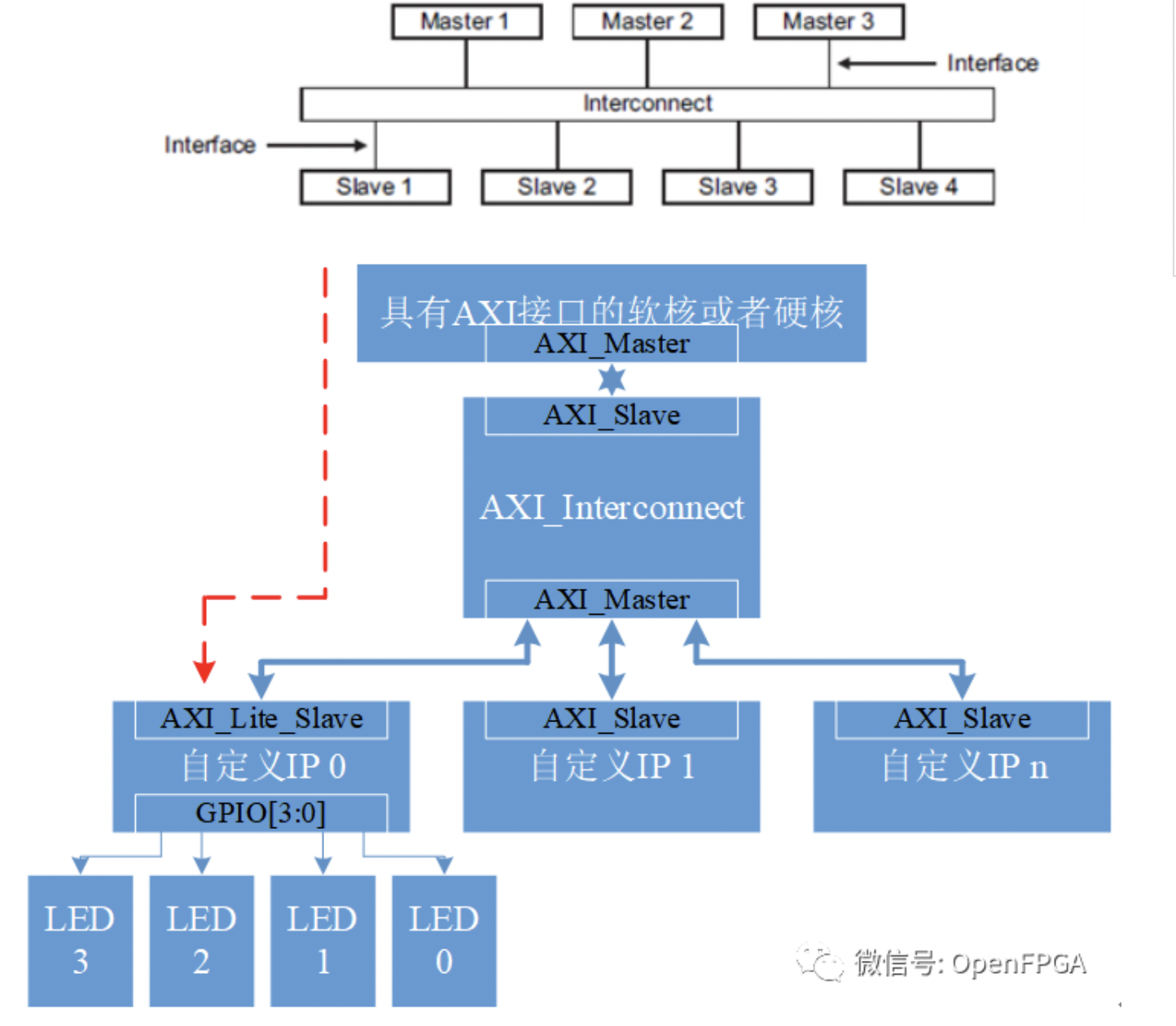

AXI-Lite 自定义IP目的:通过嵌入式软核或者硬核通过AXI_Lite接口(Master)控制FPGA端引脚的GPIO。实现框图:图4‑50自定义IP应用框图按...

AXI Stream关键的只有两根信号线,及tvalid核tready。tvalid是主设备驱动的信号,表示Stream上的数据是有效的,tready由从设备驱动,表...

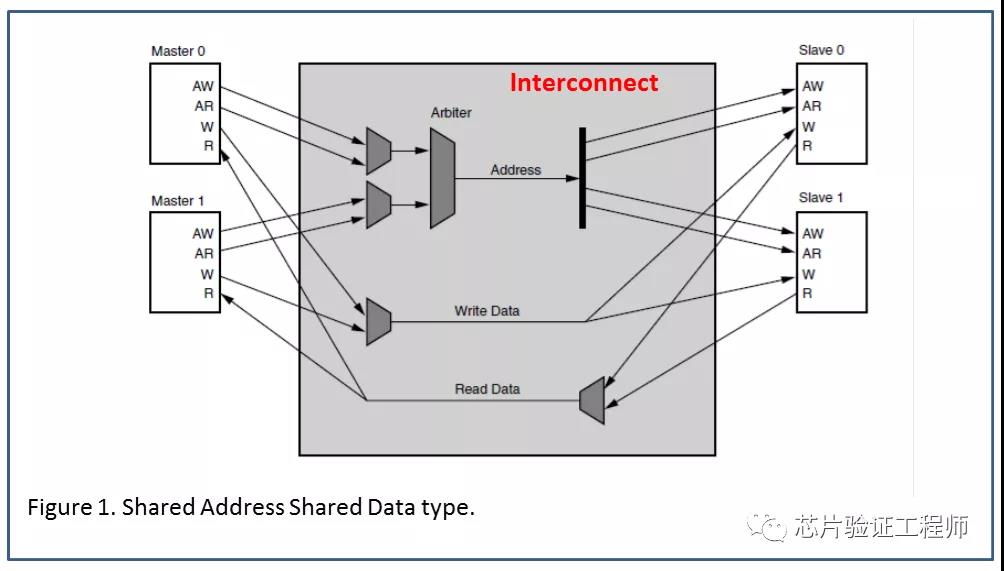

刚毕业那会研究了一段时间的3D-Torus,近期又看了CHI和CMN相关的内容,感觉互联架构挺有意思的。我想尝试做一个支持AXI协议的互联架...

AHB规范中要求所有在地址传输相位内的控制(除了HADDR和HTRANS)在突发传输周期中保持稳定。

缺点1: APB支持且仅支持一个主机 缺点2: APB两个周期才能完成一个数据的传输,数据传输效率不高。

AMBA总线是ARM研发的(Advanced Microcontroller Bus Architecture)提供的一种特殊的机制,可以将RISC处理器集成在其他IP芯核和外设中...

本指南介绍了高级微控制器总线结构(AMBA)AXI的主要特点。本指南解释了帮助你实现AXI协议的关键概念和细节。

乍一看,AMBA AXI exclusive 很容易理解,当时随着你深入研究或者经过项目的实践,你会发现这其中还是有很多惊喜的。尤其是从验证的角度...

1 .AXI3与AXI4之间的区别是什么?AXI3只支持多达16拍的burst 。而AXI4支持高达256拍的burst 。AXI3支持write interleave。AXI4不支持wri...

随着信息技术的发展,AGV(Automated Guided Vehicle,AGV)无人自动导航小车已被广泛应用于智能制造、智慧物...