要获得一个高质量的Topographical synthesis结果,需要一个良好的physical start point。

门级仿真(Gate level simulation)是对综合后,已经完成映射(mapping )到工艺库的数字设计进行验证的方法。

Verilog设计和测试平台的编码风格可能会影响仿真过程的正确(Correctness)和性能(performance),其中涉及仿真正确性的一个方面就是不...

顾名思义,模拟/全定制设计流程用于设计模拟或者全定制电路。 全定制电路是指使用晶体管,电阻和电容设计的电路,但是全定制电路不一定...

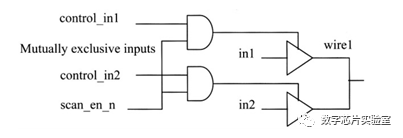

前一篇文章讨论了具有大latency 复位分配网络的高速设计复位释放的复杂性。在这里,我们讨论两种缓解此时序问题的技术。这两种技术都适...

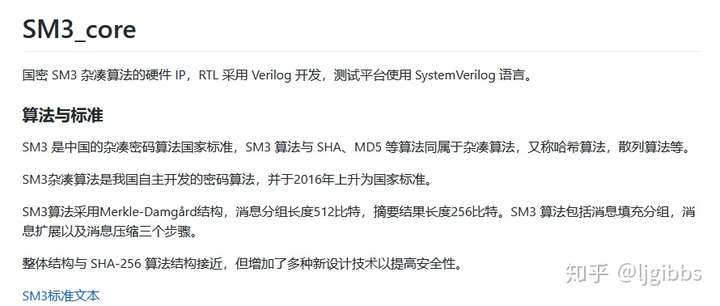

国密 SM3 杂凑算法的硬件 IP,RTL 采用 Verilog 开发,测试平台使用 SystemVerilog 语言。

之前我分享过一个代码自动格式化插件: AStyle,用过Keil的朋友应该都会安装这个插件吧!它没有图形化界面,只能作为插件在IDE中使用,还...

计算机体系结构是计算机科学与技术、软件工程等专业的核心课程之一。上这门课的老师,您还在为下学期授课准备教学资料么?如果是,那赶...

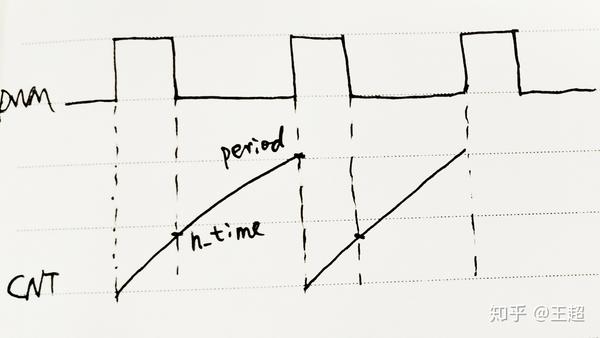

实现方法很简单,使用一个计数器一直计数,然后和两个值进行比较,一个值是高电平时间h\_time,一个值是周期period,在小于h\_time期间...

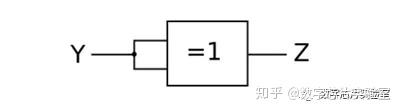

1、function中的逻辑被综合成了什么?由于function中没有任何时序结构,function只能综合出组合逻辑。例如,以下function有2个输入信号...

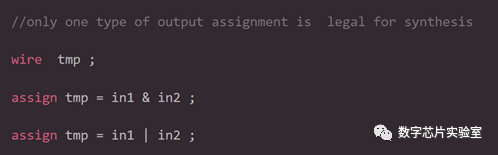

在可综合的verilog代码中,为同一个net使用多个assign语句是错误的。综合工具会报出语法错误,即“net is being driven by more than one...

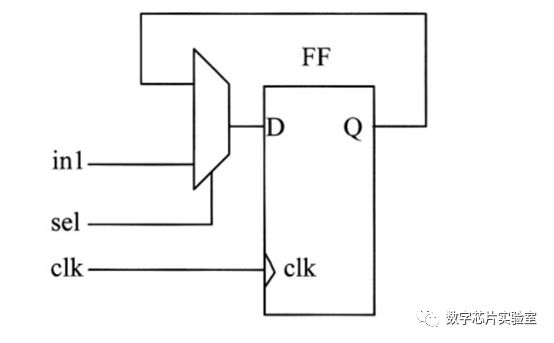

1、不同类型触发器的RTL模板从RTL中综合出的触发器或锁存器的类型取决于它们的代码风格。 以下是几个不同触发器和锁存器的RTL示例。 在...

Verilog主要有三种流程控制结构,即case,if-else和“?:”。本节主要说明了case和if-else结构的实现细节。1、如何在case语句和嵌套if-el...

有限状态机(Finite State Machines)是设计中控制逻辑的重要部分。同步状态机和异步状态机之间有什么区别?同步状态机和异步状态机是状...

本文描述了一个优化软核面积的RTL编码技术。优化掉不需要的逻辑,不仅减少了芯片面积,还减少了电路的开关活动,因此也减少了功耗。

可测试性(DFT)用来确保设计最终是可以测试的。DFT在增加故障覆盖率(fault coverage)的同时也增加了面积。

低功耗是当今大多数芯片的关键要求。 芯片的功耗越大,设备就会越热,运行速度越慢。并且在高温下,芯片的可靠性会降低。本文讨论如何在...

只有输入,没有输出的模块将被综合成什么?仅有输入且无输出的模块将会被综合成没有逻辑的模块。为什么在综合出的逻辑中看到锁存器?有...

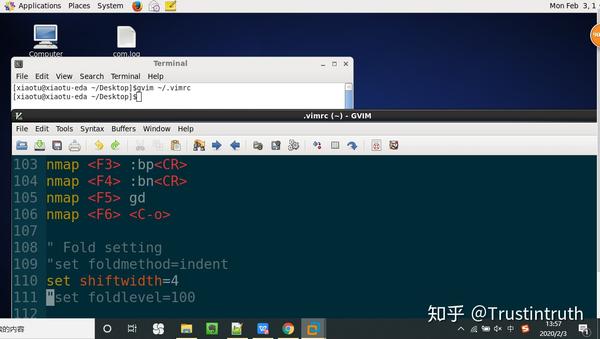

最近在学习Linux下的一些操作,在此总结gvim中的常用操作。由于许多命令用:开头,所以下面命令都是使用粗体文字。如有疏漏,还望指出。...

以下要点总结了设计阶段的主要考虑因素:1、寄存关键模块的所有输出。这将使得在系统级集成期间,接口时序很容易满足2、根据时钟域和功...