随着北斗三号全球卫星导航系统GNSS日前的正式开通,自1983年立项研究,1994年开始建设,到2020年完成,耗时37年、北斗“三步走”发展战略...

事情缘由2020年8月7日,在中国信息化百人会2020峰会上,华为消费者业务CEO余承东对外表示,因为美国第二轮的制裁,华为自研的旗舰芯片麒...

Arm中国2021校园招聘正式开启,IC设计工程师,软件工程师等岗位需求多样。2021届的毕业生们,速速投递你的简历,与我们一创造中国智能科...

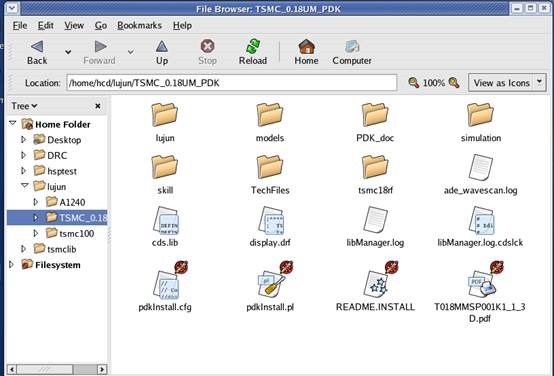

这里用的库是TSMC_0.18UM_PDK,0.18的库。从eetop下载的库。此库只可用于学习用。

VCS是synopsys的仿真verilog的仿真器。基于linux系统。有命令行模式和图形化模式。图形化模式是用的dve。

集微网(文/Kelven)如同钢铁是工业社会的粮食一般,类比过来,集成电路会是当今信息产业的粮食和动能。

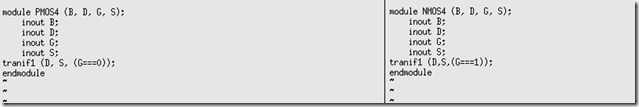

对于一个MOS电路来说,计算的话,有两个参数是比较重要的。一个是vth,一个是UnCox。不考虑其他效应。

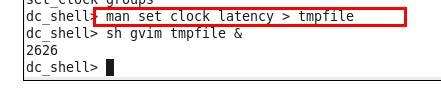

DC中,约束的时候,需要添加关于latency的约束。约束latency的命令是set_clock_latency。使用man命令,查看。这里,有个技巧,可以将man...

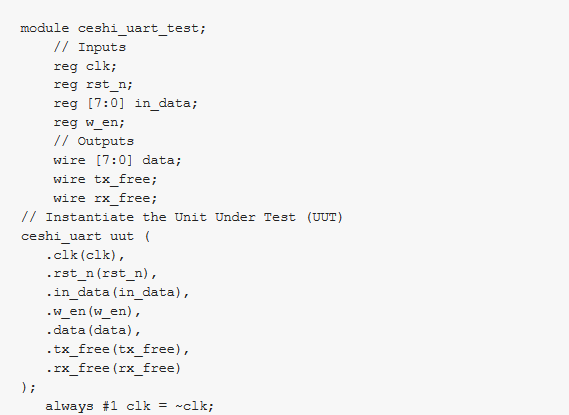

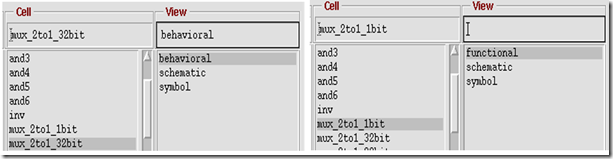

在cadence中,使用mos管和电阻构建了数字电路,但是要对这电路进行功能仿真,仿真的激励也比较复杂,不能使用简单的信号源产生,这个时...

2020-08-06 周四 20:00 开播 回顾中

NC可用于数模混合仿真,即用verilog语言给画的电路图添加输入激励信号,然后查看输出信号,以验证电路是否正确。。

如果安装的是modelsim 10.4版本的话,软件已经将UVM的库给编译好了,生成了.dll文件,供UVM验证使用。

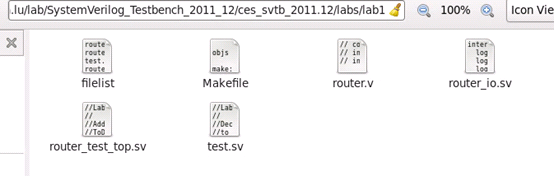

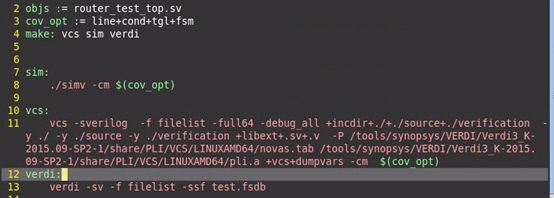

对于编写的systemverilog代码,在linux下,可以使用vcs编译,但是编译的时候,要注意,要加入几个选项。

对于vcs工具,支持生成覆盖率报告,通过查看覆盖率报告,即可知道设计中有什么问题。要生成覆盖率报告,要在编译和仿真的时候,加入一个...

综合作为后端设计中承上启下的一个环节,连接前端设计与后端PR的环节,在整个后端设计领域中占据非常重要的位置,决定了后端设计最终能...

集微网消息 光刻机是半导体制造业中最核心的设备,光刻环节能实现芯片设计图从掩模到硅片上的转移。而光刻机工件台是光刻机的核心子系统...

本文介绍CHI协议中的Cache Stashing操作和DVM操作,将分为两章节来描述。作者:谷公子

集微网消息 集微直播间自开播以来获得了大量来自行业的关注与好评。其中“集微公开课”栏目联合行业头部企业,通过线上直播的方式分享精彩...

本文描述CHI协议的properties、parameters、broadcast signals,这些指定了一个interface支持的行为。作者:谷公子

集微网(文/Kelven)在集微网举行的第十期龙门阵当中,以“异构计算带来智能互联的下一个黄金十年”为主题,英特尔中国研究院院长宋继强作...

本节描述系统一致性接口信号,用于控制RN-F是否支持Coherency和DVMdomain,以及RN-D是否支持DVM domain。作者:谷公子

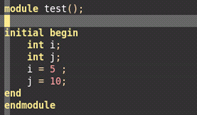

sv中,变量定义,要放在程序的最开头。比如如下:这样,编译才能成功。但是如果,变量定义没有放在最前面,而是放到了赋值语句之后,就...

INI文件是一个无固定标准格式的配置文件。它以简单的文字与简单的结构组成,常常使用在Windows操作系统,或是其他操作系统上,许多程序...

集微网(文/Kelven)自2014年《国家集成电路产业发展推进纲要》出台以来,政策的支持使得半导体行业飞速发展。从2015年开始,行业规模增...

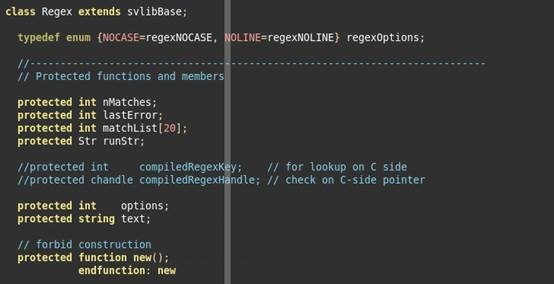

svlib中,提供了Regex类,来实现正则表达式。该类的new方法,是protected修饰的,所以该类不能通过new方法,创建对象。text:正则表达式

2020-07-23 周四 20:00 开播 回顾中

一、文件结构体对于文件,svlib提供了一个结构体sys_fileStat_s,来管理文件的属性。二、文件操作方法1. sys_fileStat函数原型:传入两...

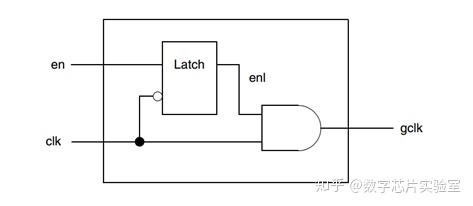

为了使用时钟门控,多电压域,多阈值库或电源开关等低功耗策略,工艺库必须包含支持这些策略的逻辑单元。 支持低功耗设计的一些单元包含...

1) VD[23:0] 24根数据线,用来传输图像信息2) HSYNC(水平同步信号)3) VSYNC(垂直同步信号):时序信号线,为了让LCD能够正常显示给的控制...

【嘉德点评】粤芯在未来将聚焦于以生物检测芯片、视频监控摄像头芯片、红外测温芯片为代表的生物安全领域,弥补国产芯片制造业的短板。