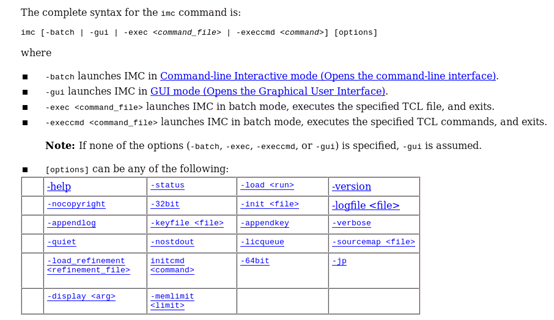

使用命令 , imc -exec commandfile 就可以启动imc的命令行程序,然后自动执行commandfile的内容,并退出。

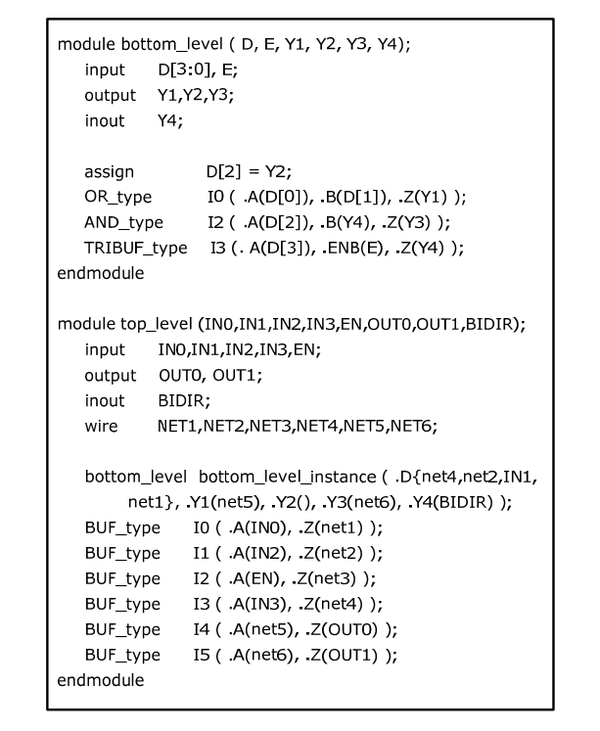

在ASIC设计的早期,逻辑设计师使用原理图或电路编辑工具设计电路。随后,出现了两种硬件描述语言:VHDL、Verilog

一、svlibsvlib,是一个开源的systemverilog的工具库。a programmer’s utility library for systemverilog官方网站这个开源库中,实现了...

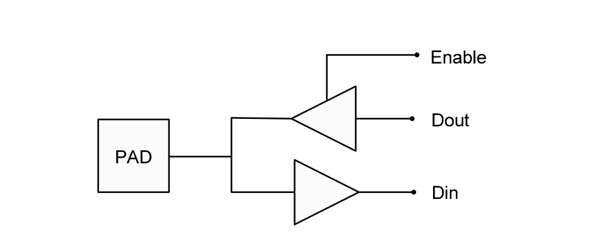

输入输出pad是ASIC后端设计中很重要的单元之一。I / O pad电路将ASIC core逻辑中使用的信号电平转换为ASIC外部的信号电平。同样,I / O ...

Google在近期搞了个芯片业的大新闻,也就是和工艺代工厂SKYWATER合作,开源了后者的Sky130 Hybrid 180nm/130nm 的PDK(Process Design K...

专用集成电路(ASIC)的数字后端设计需要各种类型的库。库是物理版图、抽象视图、时序和功能模型、晶体管电路描述的集合。

2020-07-16 周四 20:00 开播 回顾中

设计约束是ASIC电路设计规范的一种表达形式,在逻辑综合或者物理综合期间施加到设计。每个工具都试图满足两种设计约束:1、时序约束2、...

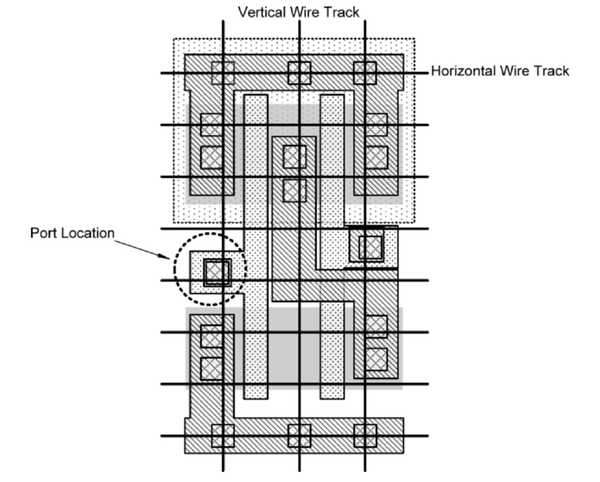

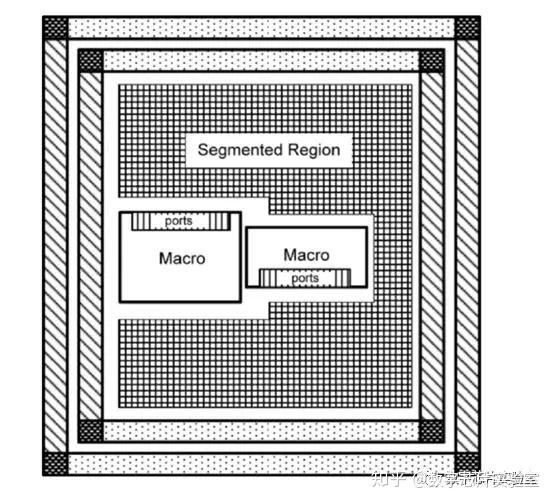

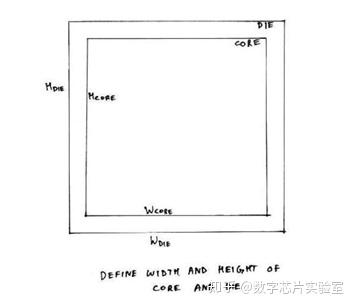

在floorplan时,需要进行宏模块placement。 这些宏模块可能是存储器或者模拟模块。在层次化物理设计中也可能是单独布局布线的子模块。 ...

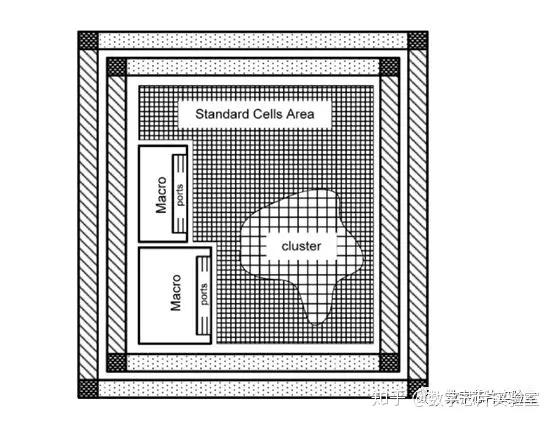

标准单元placement是ASIC物理设计中非常重要的阶段。标准单元placement的目标是将ASIC设计中的标准单元映射到core区域中标准单元placeme...

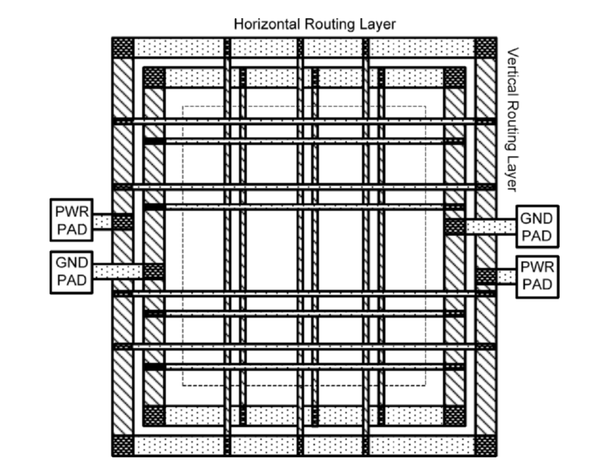

对于core逻辑,有电源和接地环围绕着core。 顶部和底部使用水平金属层,左边和右边使用垂直金属层。这些垂直和水平金属用通孔(via)进行...

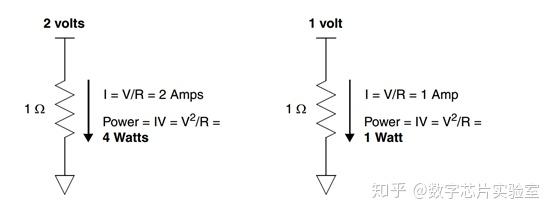

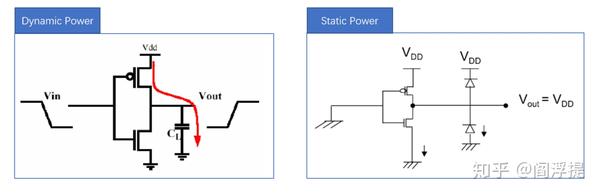

降低功耗可以从RTL-level和Gate-level设计策略着手。诸如时钟门控(clock gating)之类的方法已被广泛地使用。其他的方法,例如动态电压...

集微网(文/Kelven)潮涨潮退,千禧年伊始中美蜜月的20年已过,美国对中国全面对抗的基调短期内是不会改变。在这一大环境下,以华为为代...

在数字物理设计流程中需要对多个目标进行优化,包括面积,走线长度和功耗,以及需要确保物理实现之后的网表满足设计的时序要求。

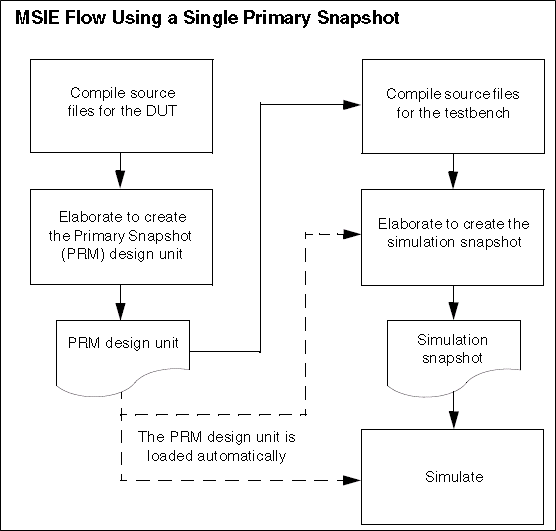

irun支持MSIE编译,MSIE的全称是 multi-snapshot incremental elaboration。将多个编译好的snapshot,组合成一个最终的snapshot,去仿真。

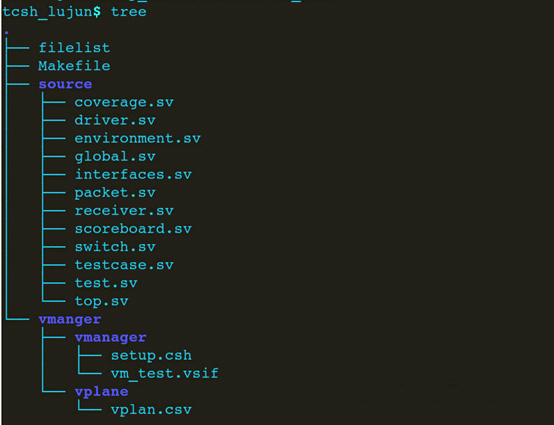

所验证的DUT,以及搭建的验证环境,是根据testbench.in网站上的systemverilog的demo来搭建的。demo的网站如下:

在“牵手”15年之后,苹果再次与英特尔上演“分手总是难免的”戏码。苹果自研Mac芯片在2020年全球开发者大会(WWDC20)上落了“实锤”,正式公...

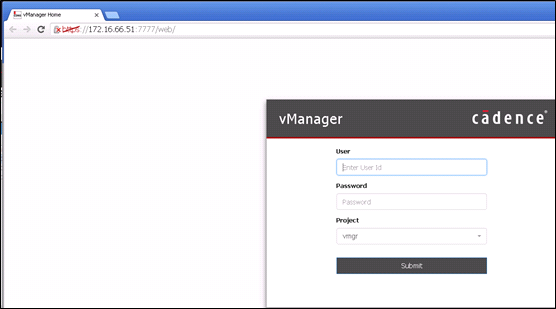

vsif(verification session input format file),是vmanager启动一个session,必备的一个文件,该文件,指定了待运行的test。vmanager...

通过vmanager连上server,可以查看各个client运行的session,以及分析run的结果,metric,反标vplan。如果只是想看结果,那就要每次启动...

最近看到一篇非常好的文章,是关于一个外国团队做了不同数字芯片实现工具的效果比较,更确切的说是Cadence和Synopsys全系列的Digital Im...

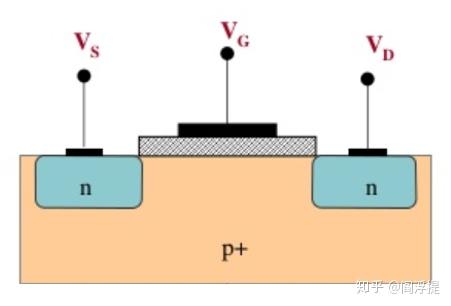

今天想和大家聊聊一种比较特别的功耗控制方法:Body Bias。由于它会涉及一些半导体器件的相关知识,我们尽量详细地从基础上向大家介绍它...

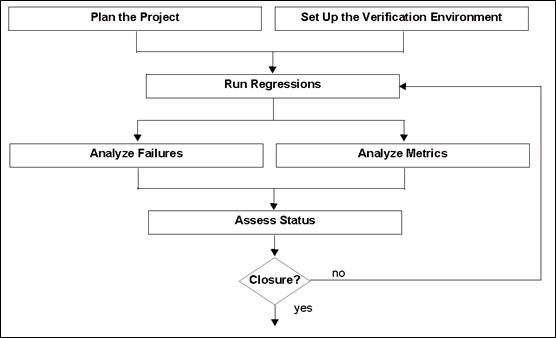

根据状态,判断,是否收敛,如果收敛,那么验证就结束了,可以signoff,如果验证没有收敛,那么就重新运行回归。

上篇文章我们讲到开源RISC-V处理器蜂鸟E203的综合之前的准备工作,包括设计的修改,floorplan def的生成,综合流程、策略和约束的设置等...

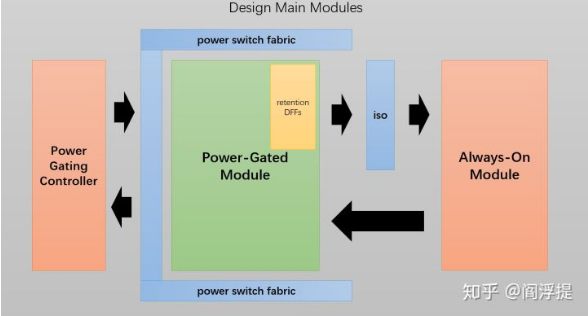

在低功耗设计领域,最有效的降低功耗的手段莫过于电源关断了。其原因在于不论多低的电压,多小的电流,多慢的速度抑或多小的leakage,都...

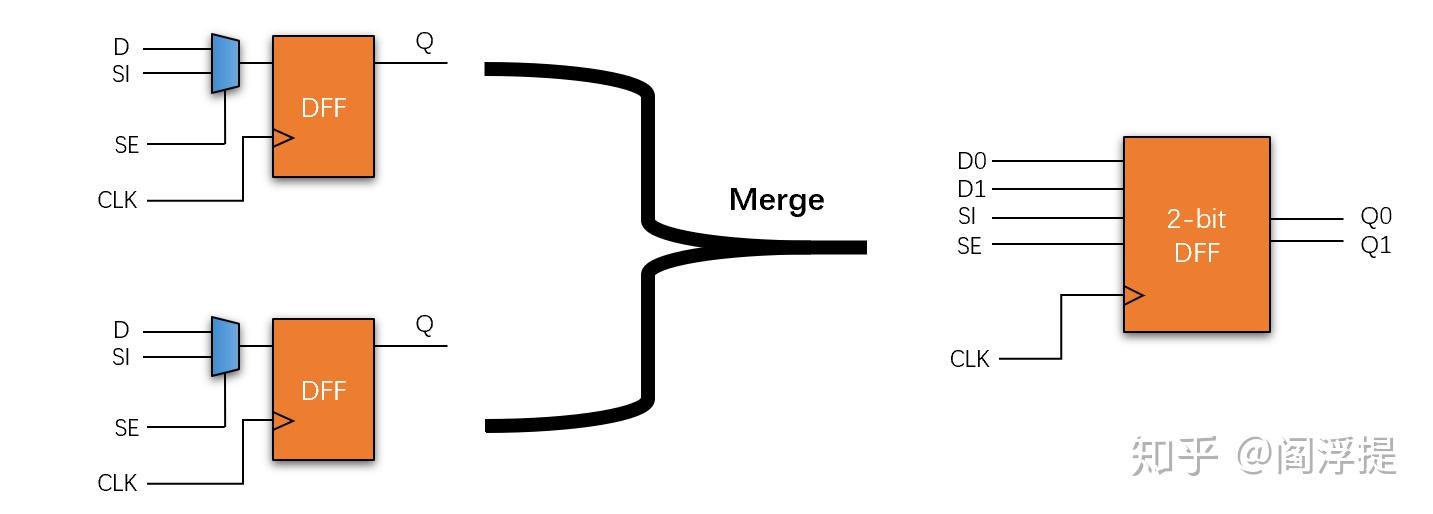

Multi-bit cells作为一种控制功耗的手段已经广泛应用于大量的芯片设计中,各种EDA工具中也提供了广泛而完善的支持。今天我们将对这种cel...

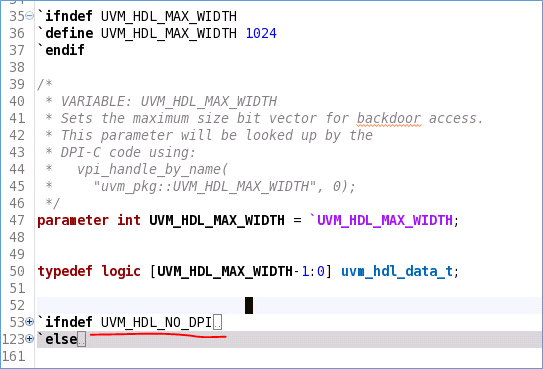

文件中,定义了使用typedef定义了uvm_hdl_data_t类型,其实就是大小为1024bit的数据。

大多数低功耗设计手法在严格意义上说并不是由后端控制的,Clock Gating也不例外。在一颗芯片中,绝大多数的Clock Gating都是前端设计者...

最近大半年IC行业的招聘市场比较动荡,不少新创公司高薪挖人,加上一些原本有成熟产品的企业也开始拉队伍自研芯片,开出了不菲的offer,...

在本系列的第一章和第二章中,我探索了如何设计可靠电源传输网络和这些网络各个要素的作用以及Arm Research如何集中精力利益最大化此类...

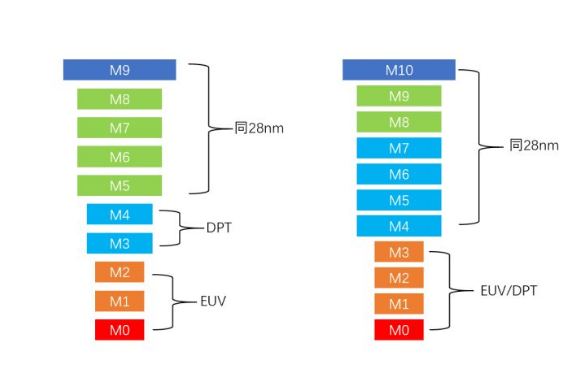

最近开始做一个7nm的项目,发现对于后端来说,有一些东西和之前的工艺有些不同,因此希望借此机会和大家分享一下。