思考:在页表的Descriptors中的Lower attributes中的AttrIndx中指向的MAIR_EL1寄存器中有配置cacheable属性, 在TCR_EL1寄存器中有cachea...

缓存替换策略是用于确定在缓存空间已满时应该替换哪些缓存项。Pseudo-LRU(Pseudo-Least Recently Used)和LRU(Least Recently Used)...

内存屏障(Memory Barrier)和缓存(Cache)之间有密切的关系。它们都是计算机系统中用于确保内存操作顺序和一致性的重要概念。

我们知道每一个Arm core的L1/L2/L3的cache是多大的,要么是IP定死的,要么是ASIC可配置的。那么从性能角度来说,是不少配置的越大越好呢...

思考:REE刷TLB时会把安全的TLB刷掉吗?TEE刷TLB时能否刷安全的TLB?例如页表管理着的共享内存,它的翻译缓存到了TLB.

在人工智能的淘金热中,英伟达吃肉,小型关键参与者喝汤。这次我们要说的是正发力在Retimer这个小型芯片的供应商。目前一台典型的配8块G...

3月20日,上海国际半导体展览会SEMICON China 2024盛大开幕。作为中国规模最大的半导体业界盛会之一,SEMICON China囊括了当今半导体制...

芯片是科技发展的核心关键和技术底座。当下RISC-V、Chiplet、AI、汽车电子等成为该行业的高频词。这两年的半导体行业,皆围绕着这几个技...

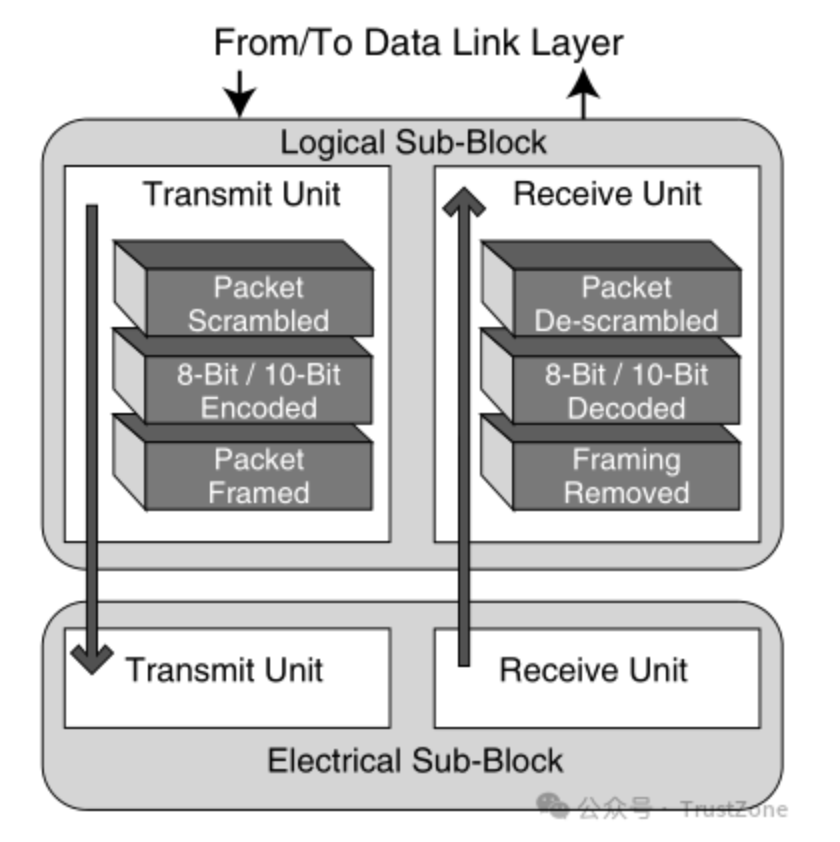

在看完事务层和数据链路层之后,我们来继续我们的协议栈之旅吧!这一篇中,我们会来看看PCIe物理层(Physical Layer)是如何工作的,从...

引流关键词:缓存,高速缓存,cache, CCI,CMN,CCI-550,CCI-500,DSU,SCU,L1,L2,L3,system cache, Non-cacheable,Cacheable, non-shareable,i...

思考:在经典的 DynamIQ架构 中,数据是什么时候存在L1 cache,什么时候存进L2 cache,什么时候又存进L3 cache,以及他们的替换策略是怎...

思考:1、为什么要学习MESI协议? 哪里用到了?你确定真的用到了? 2、MESI只是一个协议,总得依赖一个硬件去执行该协议吧,那么是谁来维...

引流关键词:缓存,高速缓存,cache, CCI,CMN,CCI-550,CCI-500,DSU,SCU,L1,L2,L3,system cache, Non-cacheable,Cacheable, non-shareable,i...

引流关键词:缓存,高速缓存,cache, CCI,CMN,CCI-550,CCI-500,DSU,SCU,L1,L2,L3,system cache, Non-cacheable,Cacheable, non-shareable,i...

在学习MMU章节时,我们发现在页表的entry中,BIT[4:2]指向了MAIR寄存器,该寄存器描述了内存属性,其实就是cache的缓存策略属性(inner\...

ARM 架构刚开始开发时,处理器的时钟速度和内存的访问速度大致相似。今天的处理器内核要复杂得多,并且时钟频率可以快几个数量级。然而...

cache里都有什么? 或者问cache line(即每个entry)里都有什么?答案是 : TAG + DATA + invalid bit + dirty bit那么TAG里又都有什么呢?

网上的好多篇博文,一提Cache的多核一致性就必然提到MESI、MOESI ,然后就开始讲MESI、MOESI维护性原理?试问一下,您是真的不理解MES吗...

场景:CPU往src地址处写入了一串数据,然后交给Crypto硬件进行加解密处理,加解密后的数据放在了dst地址处,然后cpu读取dst地址处的数据...

装饰器模式(Decorator)是一种结构化软件设计模式,它提供了一种通过向类对象添加行为来修改类对象的方法,而不会影响同一类的其它对象行...

编者按:最近,围绕着垂直式GaN发生了很多新闻,例如去年年底,NextGen system的倒闭以及最近Odyssey semiconductor的清盘。这就不禁引...

功率半导体赛道火热,尤其受到电动汽车与能源行业的热烈追捧。那么,如何确保功率半导体的性能呢?关键在于精准测试。NI将在SEMICON(NI...

不少粉丝问我这个问题,今天我们就来给大家分析下。首先说下结论,IP DV的需求会越来越少,SOC DV则不会,如果有得选尽量选SOC DV。为什...

思考为什么要用虚拟地址?为什么要用MMU?MMU硬件完成了地址翻译,我们软件还需要做什么?MMU在哪里?MMU和SMMU是什么关系?

本文转自 周贺贺,baron,代码改变世界ctw,Arm精选, 资深安全架构专家,11年手机安全/SOC底层安全开发经验。擅长trustzone/tee安全产...

armv8定义了device memory和normal memory两种内存,其中device memory固定的就是Outer-Shareable和Non-cacheable,而normal memory有多...

本文转自 周贺贺,baron,代码改变世界ctw,Arm精选, armv8/armv9,trustzone/tee,secureboot,资深安全架构专家,11年手机安全/SOC底...

操作系统中可能存在多个任务, 内核调度器周期性地将执行从一项任务转移到另一项任务。在这个过程中,操作系统会保存上一个进程的执行状...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈1、TCR寄存器介绍在ARM Core中(aarch64),还有几个相关的系统寄存器:TCR_EL1TCR...

Log2 of the number of words in the smallest cache line of all the data caches and unified caches that are controlled by the PE.x