在我工作中曾经帮助一些客户定位和解决芯片SoC硬件,CPU挂死问题这类疑难杂症。这类问题在被报告的时候,通常表现为软件不正常工作,例...

版权声明:本文作者:烓围玮未。主要从事ISP/MIPI/SOC/车规芯片设计/SOC架构设计知乎专栏:芯片设计进阶之路微信公众号:芯片设计进阶之...

本期我们学习一篇讨论 DDR4 板级设计和信号完整性验证面临的挑战的论文,由来自西门子、富士通以及美光等公司的作者联合完成。

本系列连载于 OpenIC SIG,除了 DDR 学习时间专栏外,OICG 目前正在陆续上线 HDLBits 中文导学的优化版本,欢迎关注/支持/加入我们

本期我们学习一篇关于 DDR IP 硬化(Hardening)的文章,讲述了在 DDR IP 后端实现中的一些建议。笔者在 AI 翻译的基础上对译文进行修正...

EDA工具的log(日志)捕获,是一个经常会用到的功能,有助于用户查看long run job的状态和错误捕获,这里一般是利用了linux下的重定向(...

Xcelium使用命令行选项来启用和控制低功耗仿真。所有与低功耗仿真相关的命令选项都以-lps_前缀开头的。

Type[7:0] 表示了TLP Header Base的类型和Size。TLP Header Base之后紧跟的0到7DW的Orthogonal Header Content (OHC) 内容则由OHC[4:0]...

之前有位读者让聊聊AUX协议,可能是因为之前讲DP,没有深入这部分,于是今天专门在节前整理点资料,聊聊这个。

作者 | 北湾南巷出品 | 芯片技术与工艺在集成电路(IC)设计领域,版图与原理图一致性检查(LVS,Layout vs. Schematic) 是确保设计准...

对于非微电子专业做FPGA的同学们来讲,常常把仿真验证环境的搭建给忽略了,为了追求所谓的“高效”,自己写的代码根本就没怎么仿真验证过...

随着数据传输速度迈入多千兆比特级别,数字系统的复杂性急剧增加。在加快产品上市速度的同时,如何保证设计的准确性和可靠性,成为工程...

生成事务层数据报文(TLP):接收设备核心层(Device Core)的数据请求(如数据读写、完成反馈、信息传递等),将其转换为标准的 PCIe ...

在进行编码时,我们时常会使用到乘法器,除法器,等较复杂功能模块,为此 fpga vendor 设计定制了 IP 核,用户通过调用 IP 核来实现所需...

在先进工艺驱动芯片不断朝向更高性能、更小尺寸演进的时代,ASIC 封装早已不再是设计流程中的“最后一步”,而成为与芯片设计同步推进、紧...

锁相环(PLL)是通信和时钟系统的核心模块,其设计需在噪声、功耗、面积等多维度权衡。本文基于ISSCC 2021课程内容,系统梳理PLL的设计...

在当今数字化时代,芯片作为现代科技的核心,其复杂度和重要性都在不断攀升。从智能手机到 AI,从汽车电子到 IOT,芯片无处不在,而其质...

关键词:LLM 定制,RTL 设计,VHDL 设计,LLM as a Judge,高性能处理器设计生产力

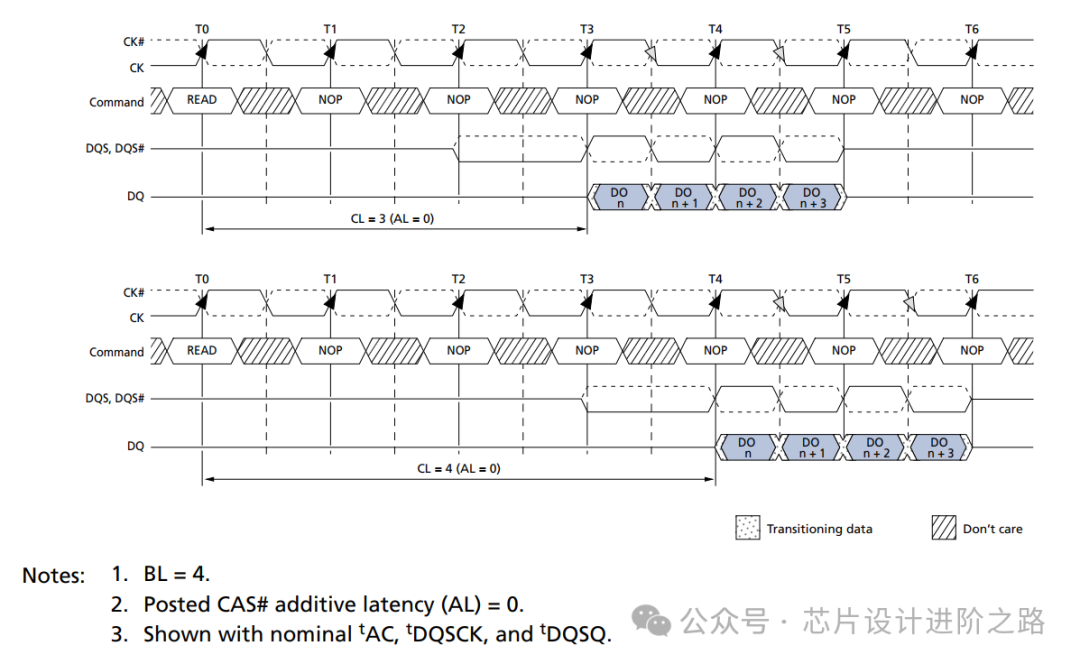

在学习了比较简单的DDR3的大部分知识后,我们来增量的学习DDR4/DDR5,然后再去研究一下DDR控制器。

随着芯片复杂度飙升(动不动几十亿晶体管),FPGA加速场景爆发(AI、自动驾驶、6G),总线协议和片上互联早已从“纸上谈兵”变成工程师的...

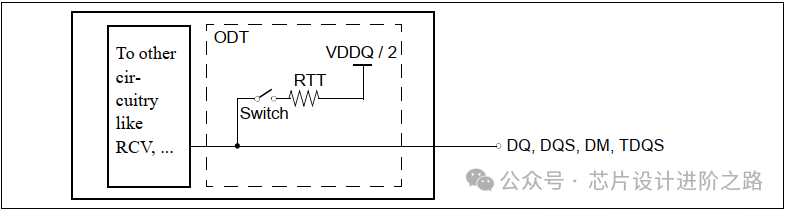

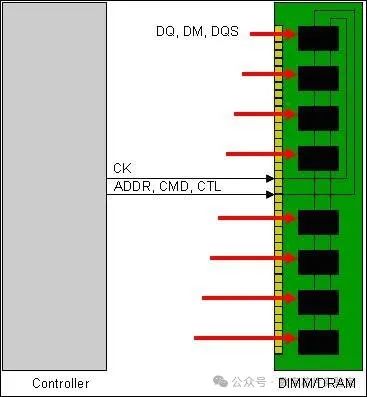

在 DDR 技术的演进过程中,ODT(On-Die Termination)和 OCD(Off-Chip Driver Calibration)成为了确保信号完整性和提升数据传输效率的...

小米在其15周年战略发布会上推出自研旗舰SoC芯片“玄戒 O1”,这是小米十余年芯片研发历程进入关键转折点。

虽然目前世界上都在推行可读性好、可维护性好的 RTL 编码规则,一大堆公司机构也都推出了各种各样的编码规范,网上一搜索各种好的编码规...

SoC 芯片(System on a Chip,片上系统)是一种将多个电子系统功能集成到单一芯片上的集成电路。它通常包含中央处理器(CPU)、图形处理...

2024年AMD发布了变化巨大的一代微架构Zen5,并宣称Zen5微架构是未来几代微架构的基石。相比较Zen4,Zen5的IPC增加了16%,这个增长非常可...

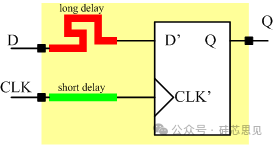

现代 SoC 设计通常采用多个时钟,并包含多个时钟域。当数据从一个时钟域跨越到另一个时钟域时,由于异步时钟域交叉(CDC),会出现亚稳态...

今天和大家分享一下 DDR 内存设计中一个重要的技术 - 写平衡(Write Leveling)。这项技术对于高速 DDR 内存的正常工作至关重要。

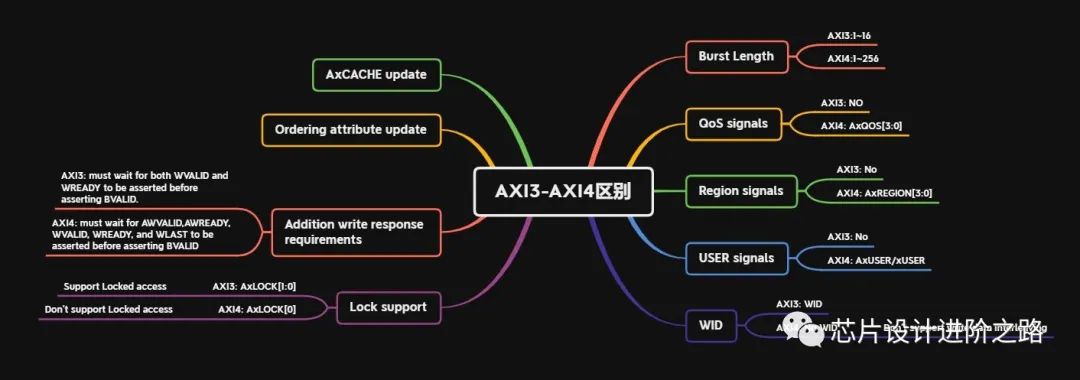

在 SOC 各种总线中,AXI 是最重要的总线,没有之一。不管是在工作中,还是在面试中,AXI 协议是一个必须精通的知识点。ARM 从 AMBA1 到 ...

全球电动工具市场规模近年来保持稳定增长,2023年市场规模已达288.5亿美元,预计2024年将突破304.9亿美元,年复合增长率达6.9%。中国市...

在当今这个数据驱动的时代,内存子系统的性能对各种计算系统的表现起着至关重要的作用。DDR(Double Data Rate)内存技术自 2000 年推出...

在进行后仿真时,经常会看到工具反标时提示存在负延迟,并且这些负延迟经常出现在 SETUP、HOLD、INTERCONNECT 和 IOPATH 中。出现负延迟...

VHDL 的 英 文 全 名 是 Very-High-Speed Integrated Circuit Hardware DescriptionLanguage,诞生于 1982 年。

“每天用手机刷视频、打游戏、扫码支付的你,可能从未意识到:掌心里的这块‘玻璃板’中,藏着一座堪比北京地铁网的超级迷宫——它就是手机芯...

在使用静态时序分析工具的时候,通常会遇到 case analysis 的情形,但是由于时序分析工具的静态分析属性,工具会自动传播 case value,...

Chiplets 技术将大型集成系统级芯片(System-on-Chips, SoC)分解为更小的功能模块,有望为半导体行业带来革命性变革。通过允许不同公司设...