在逻辑设计时,有这么一个场景很常见:对于输入的一组总线,我们需要改变其中的某些信号的赋值,而其他信号保持不变输出。正如下面的设...

众所周知,SpinalHDL仿真目前仿真器首推Verilator,无论是在Mac还是Linux下安装都很轻松,唯独在Windows下安装是一件令人头疼的事情,由...

在前面的五篇文章中,对于Axi4总线互联的所有设计细节都已经做了介绍。那么剩下的就是集成工作了。再来回顾整个总线互联架构:

RTA-OS是基于OSEK OS的符合AUTOSAR规范的OS,是一种静态可配置、抢占式实时操作系统(RTOS),用于高性能、资源受限的应用程序。

【嘉勤点评】小鹏汽车的泡水报警专利,通过获取水面图像的频率判断车辆是否淹水并报警,既可以非接触地获得摄像头与水面的距离,又能够...

在本指南中,我们向那些不熟悉Neon的程序员演示了如何在代码中使用本征来实现单指令多数据(SIMD)处理。以这种方式使用Neon可以带来巨...

本文聊一下如何在 GPU CUDA 编程里使用 memory padding 来避免 bank conflict。

比如,Pre-Switch 采用的方式是使用AI来控制SIC器件,将逆变器开关速度提高,来减少驱动系统的损耗,从而实现更大的 EV 续航里程。

所谓"外部" 的中断信号,要看有多"外"。有在cpu外面,但是仍然是芯片里面的,比如uart,i2c,pwm,timer,看门狗等总线上挂接设备发的中...

来源:内容由半导体行业观察(ID:icbank)编译自sparrowsnews,谢谢。 在最近的联发科技术峰会上,联发科调侃称将在CES2022展示下一代W...

HDMI 论坛的成立是为了促进更广泛的行业参与下一代 HDMI 规范的开发,并支持可互操作的 HDMI 产品生态系统。HDMI 规范在单个数字接口中...

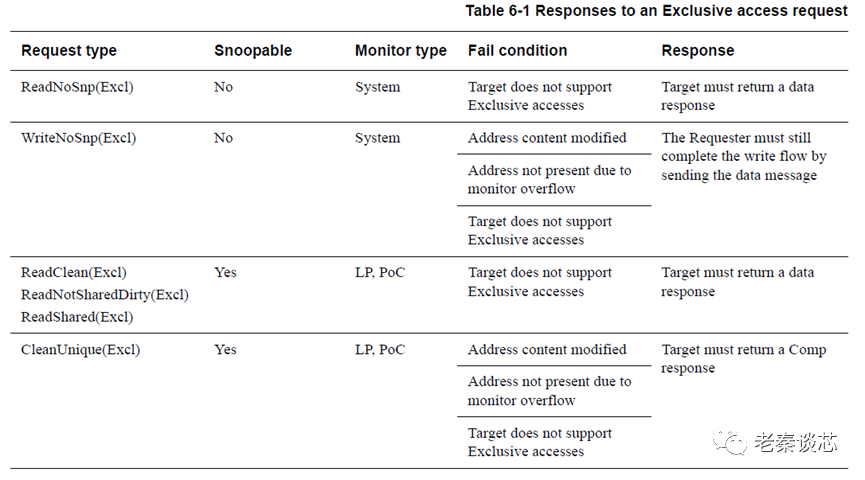

什么是独占访问呢?就是处理器对某个内存地址的数据,在某个时间段内享有独有的访问。为什么要有独占访问,或者说何时需要独占访问呢?...

局上,有个业内大佬兴致勃勃的介绍他新的创业项目,人工智能芯片,大佬说是采用一种“颠覆式”的核心技术,能够颠覆现有的AI芯片架构。

来源:内容由半导体行业观察(ID:icbank)原创,作者:李飞,谢谢。 最近,AMD正式发布了其Instinct MI200系列GPGPU加速卡,进一步进军...

按照IC Insights统计,由于Covid-19大流行导致的习惯改变,以及随后的经济反弹,预计2021年全球半导体市场将增长23%,半导体单位出货量...

本文主要记载如何从零开始在win平台搭建SpinalHDL开发环境并跑通第一个spinal project demo。

灵动微MM32系列单片机为用户提供了丰富的选择,可适用于工业控制、智能家电、建筑安防、医疗设备以及消费类电子产品等多方位嵌入式系统...

联发科过去几年一直被普遍认为是移动SoC供应商的第二选择,因为大多数媒体和消费者的注意力都集中在苹果、高通、三星和海思等公司的旗舰...

来源:内容由半导体行业观察(ID:icbank)编译自semianalysis,作者:Dylan Patel,谢谢。 通过在光刻图案的分辨率上提供阶跃函数增加...

【嘉勤点评】泰矽微发明的利用ROM结合存储孤岛实现MCU芯片安全的方案,利用加密技术以及云端存储技术,只有解密ROM启动单元才能读取到存...

在处理繁重的计算工作负载时,如ML推理,优化和剖析是必不可少的。它需要正确的方法,也需要正确的工具。本教程演示了如何使用Arm Strea...

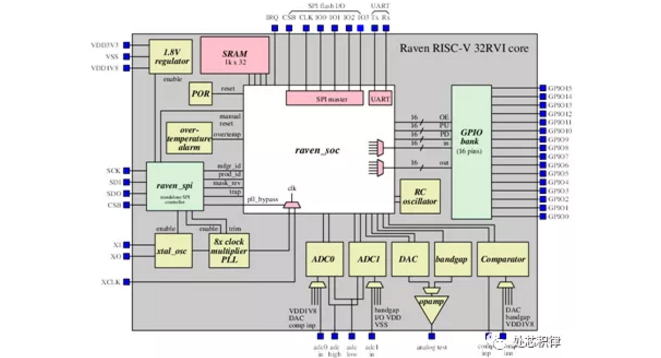

最近听到粉丝说没有项目可以实践。作为处芯积律公众号的粉丝怎么能没有项目呢?今天我和大家分享一个之前谈过的开源项目,能不能吃得下...

很多人对罗伯特·诺伊斯这个名字很陌生,但是你一定不会对“英特尔”这个名字感到陌生。是的,他就是Intel创始人-罗伯特·诺伊斯。

相较于Axi4写通路,多通路的多选一就容易多了。对于Axi4ReadOnlyArbiter,其仅需处理两个问题:

Decoder解决了一拆多的问题,那么Arbiter就需要解决多选一的问题。对于写通道,axi4有aw、w、b三个通道,相应地Arbiter就需要解决:

对于Axi4读操作而言,其指令的完成由ar、r两个通道完成,相较于写操作,其通道数虽然少了一个,但也是两个方向的数据流:

O_o >_< o_O O_o ~_~ o_O

随着新能源汽车、自动驾驶、家电等领域需求的快速增长,最为紧缺的28nm及以上成熟制程芯片的供应似乎成为关注的焦点。

在2021 年 10 月发表在美国化学学会期刊《应用纳米材料》上的一篇论文中,工程师们揭示了一种特殊合成的硼烯(Borophene)的超导特性。...

安卓和Linux版本的Mali GPUs设备驱动提供了对属于Bifrost系列的Mali GPUs的低层次访问。