上一篇文章讨论了片上网络的研究需求,经过朋友圈转发以后引起了大家的一些热议和讨论。很多朋友急不可耐的催更,也有一些朋友提出了一...

为了不拖更,现在也只能把原来比较宏伟的写作计划往简化了去搞。(此处应该有一配图,但是找不到那张图了所以先暂时空在这里)目的呢还...

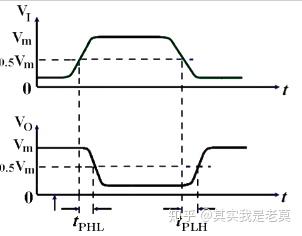

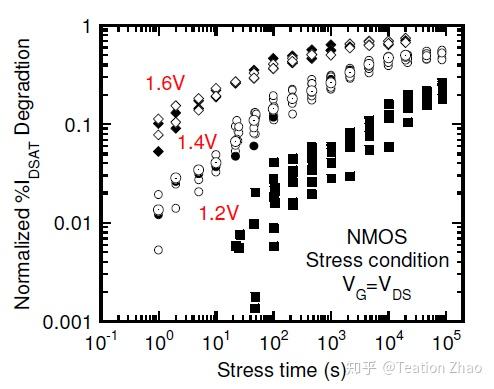

晶体管的老化效应主要是HCI与NBTI已经是无需争论的事实,而HCI在电路中主要受到信号翻转率(SA,Switch Activity)的影响,而NBTI主要受...

ISSCC全称为IEEE International Solid-State Circuits Conference(国际固态电路会议),被誉为集成电路领域的"奥林匹克"。会上开放大量...

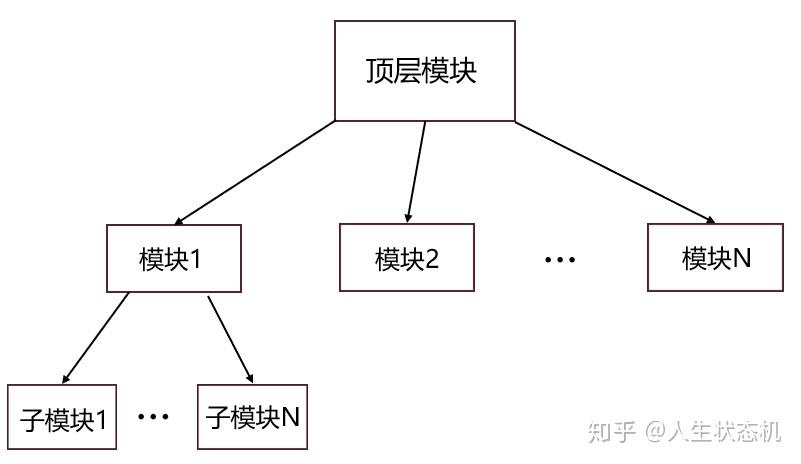

FPGA最初只是作为一种“粘合逻辑”,来实现不同芯片之间的连接和扩展。随着FPGA规模的扩大,其内部具备的查找表、乘法器、嵌入式存储器等...

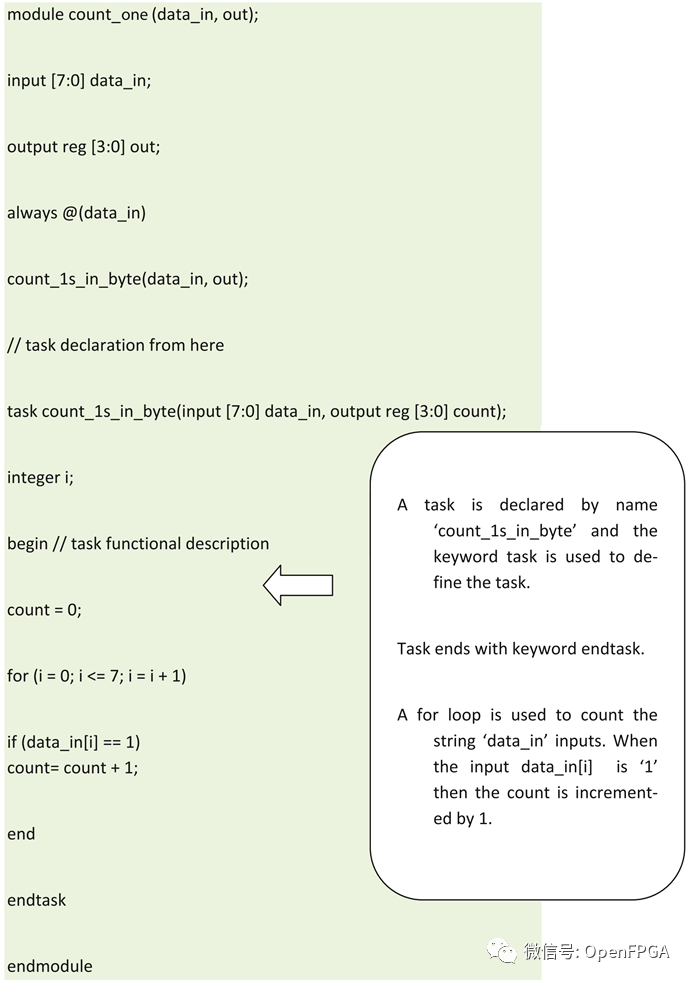

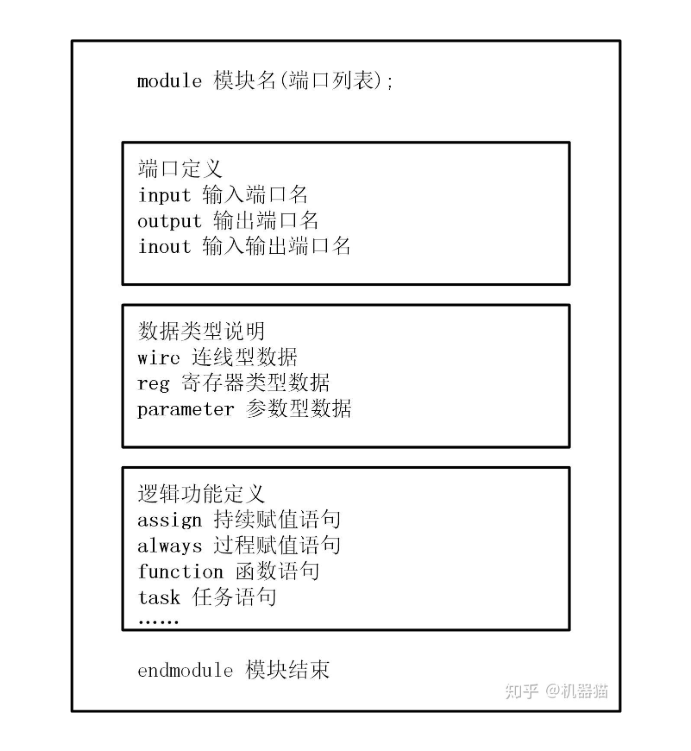

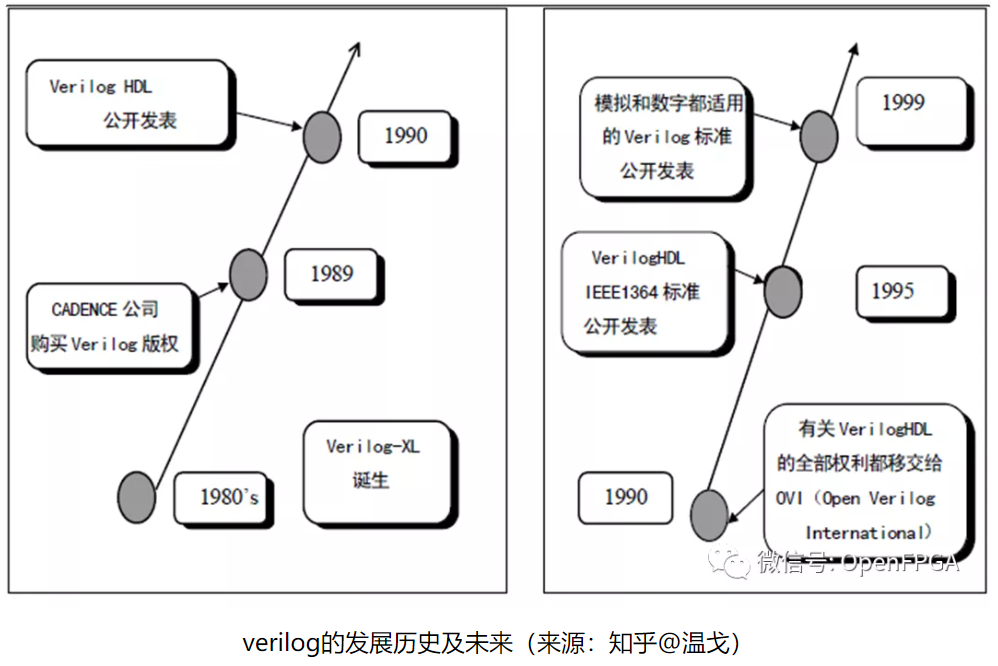

由于本实验的硬件设计部分使用 Verilog HDL 编写, 考虑到很多同学之前并没有接触过 Verilog 或者是使用的 VHDL 语言进行设计, 故本章主...

使用Verilog可以方便地实现复杂的设计。现在,设计复杂性增加,设计需要针对低功率、高速和最小面积进行优化。

在上一篇文章中已经介绍了简单组合逻辑在FPGA开发板上的实现,包括大家熟悉的优先编码器、多路复用器和全加器等,文章链接如下:

• 【玩转Arm-2D】不到4K RAM的自制FlappyBird 竟然快到我跟不上本文介绍了如何使用Arm-2D图形引擎在树莓派Pico开发板上快速制作一款时下...

1.Verilog模块基本结构2.词法(Lexical tokens)2.1空白符(White space)空白符包括空格、制表位(tab)、换行、换页。2.2注释(Commen...

杰哥找这张图表的出处找了很久,网上各路新闻都说图表数据来源于人才解决方案公司翰德(Hudson)于1月19日发布的《2022人才趋势报告》[1...

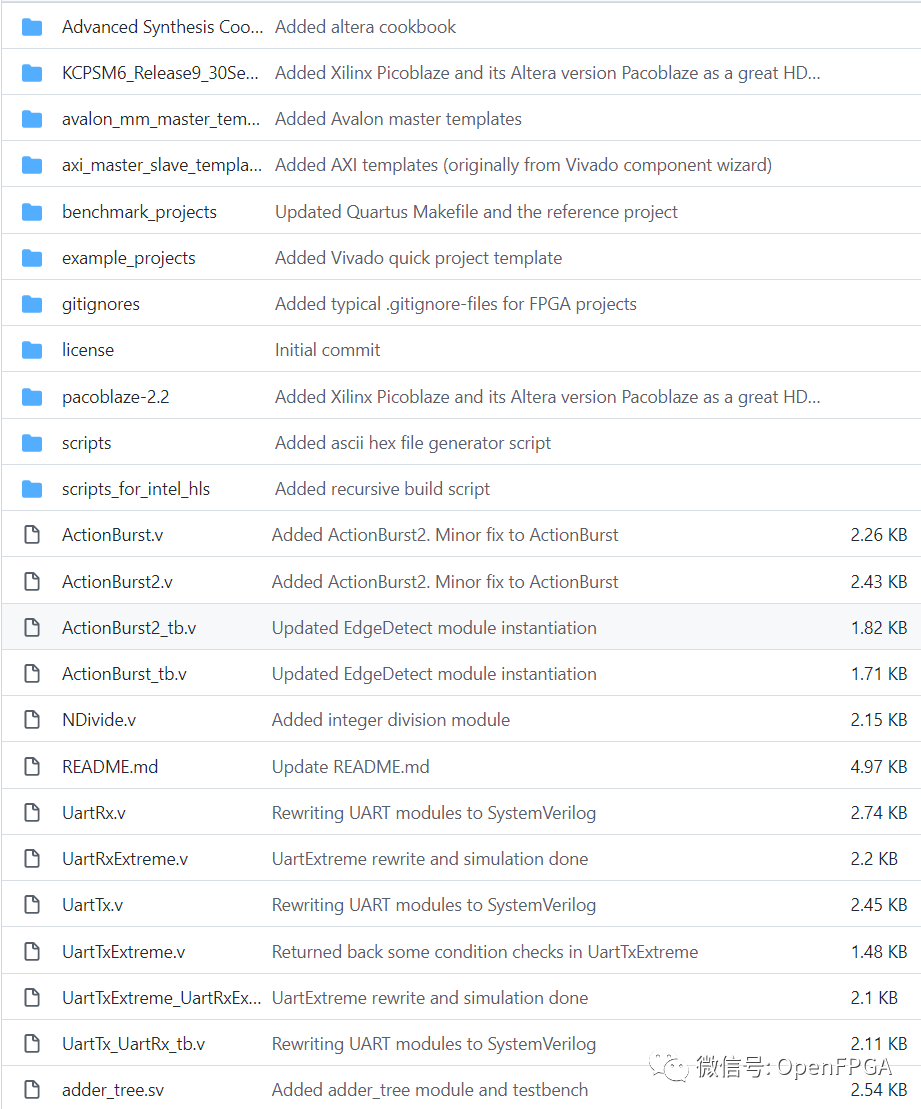

想拥有自己的Verilog IP库吗?设计时一个快捷键就能集成到自己的设计,酷炫的设计你也可以拥有!

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

5年半的外企工作经历见证了杰哥从学生到职场人的转变,见证了杰哥从初级工程师到资深工程师的提升。期间有很多重要的时刻、很多有意义的...

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

AHB规范中要求所有在地址传输相位内的控制(除了HADDR和HTRANS)在突发传输周期中保持稳定。

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

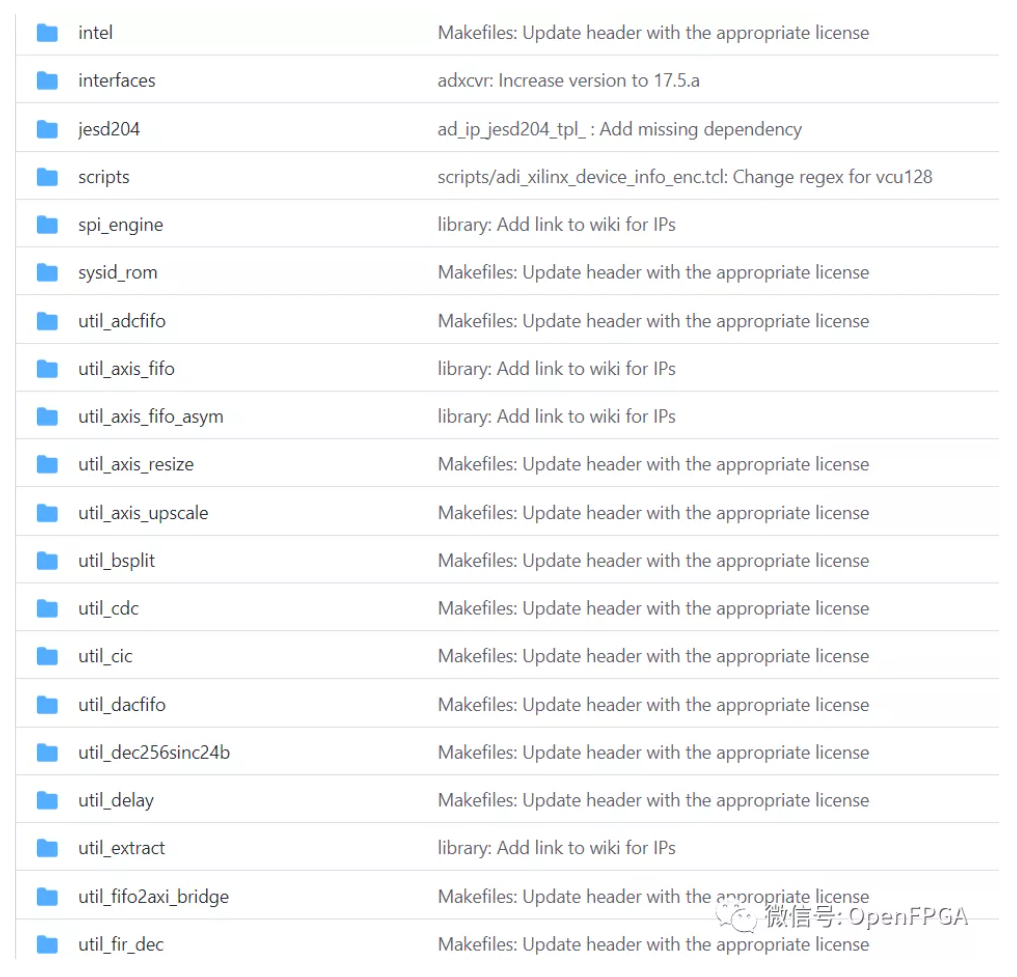

官网[链接]github[链接]HDL 参考设计Analog Devices Inc.用于各种参考设计和原型系统的 HDL 库和项目。该存储库包含 HDL 代码(Verilog ...

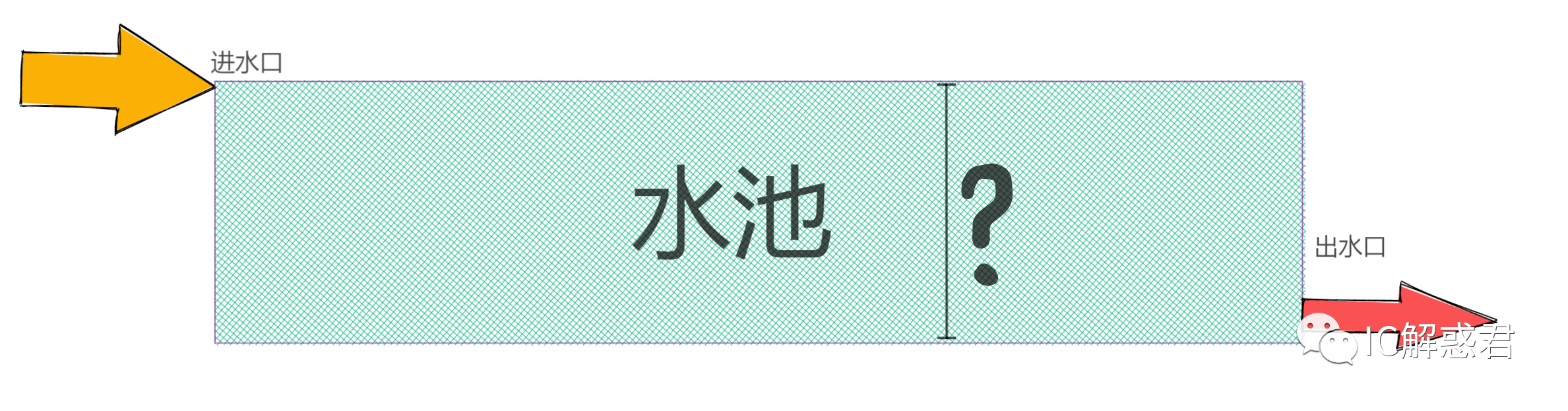

最近加的群里面有些萌新在进行讨论FIFO的深度的时候,觉得FIFO的深度计算比较难以理解。所以特出漫谈FIFO系列,会涉及到FIFO的深度计算...

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

2022 年开年,思必驰旗下的芯片设计企业深聪智能(全称:上海深聪半导体有限责任公司)宣布完成上亿元人民币的 A 轮融资。雅迪科技集团...

Verilator是一个 Verilog 仿真器和 C++ 编译器,它还支持 linting:静态分析设计问题(代码校验工具)。Verilator 不仅可以发现综合工具...

.*将会匹配多个字符串,所以u5.ux将被匹配到,最终输出结果会是"[UVM_MATCH_SUCCESS]"。

1.always@后面内容是敏感变量,always@( * )里面的敏感变量为 * ,意思是说敏感变量由综合器根据always里面的输入变量自动添加,也就是...

在开发流程中,设计和验证人员关注的点肯定是不一样的,尤其在spec的理解上,验证人员往往需要有自己独立的理解。在拿到spec时,作为验...

SystemVerilog标准(SV-2009)发布距今已近十余年,在验证领域已经大放异彩,但是在设计领域(尤其FPGA领域)使用的还是比较少,虽然市...

一个完整的vivado工程往往需要占用较多的磁盘资源,少说几百M,多的甚至可能达到上G,为节省硬盘资源,可以使用Tcl命令对vivado工程进行...

• 安谋科技"星辰"STAR-MC1处理器初探本视频为安谋科技“星辰”STAR-MC1处理器系列webinar第一期回放视频,该视频围绕着 "星辰"STAR-MC1处...

01 如何在子类中调用父类的task?可以在子类中使用super关键字引用父类中的成员,尤其是该成员已经被子类覆盖。 {代码...} 仿真结果: {...

queue(队列)是一个可变大小的、有序的元素集合,类似于自动增长和收缩的一维数组。队列可用于建模先进先出缓冲或者先进后出缓冲。