在SV中可以使用结构体作为模块的输入或输出,这使得它可以更加清晰地传递更多的信号,以简化RTL代码,类似于interface。

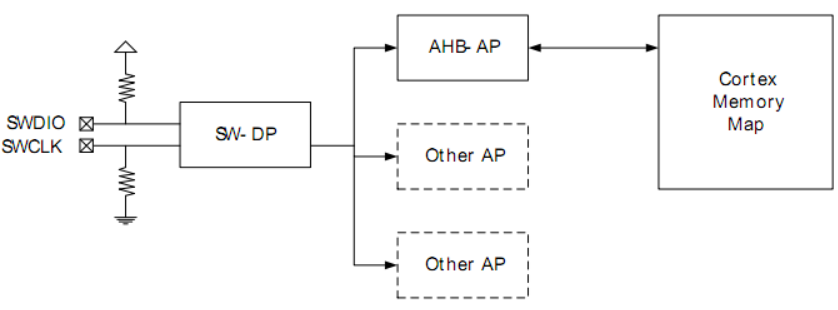

前言ARM的文档写的已经很好了,但是关于上电以后的第一时间应该怎么操作,依然写的不够清晰,导致我第一次用的时候还是费了一些周折。今...

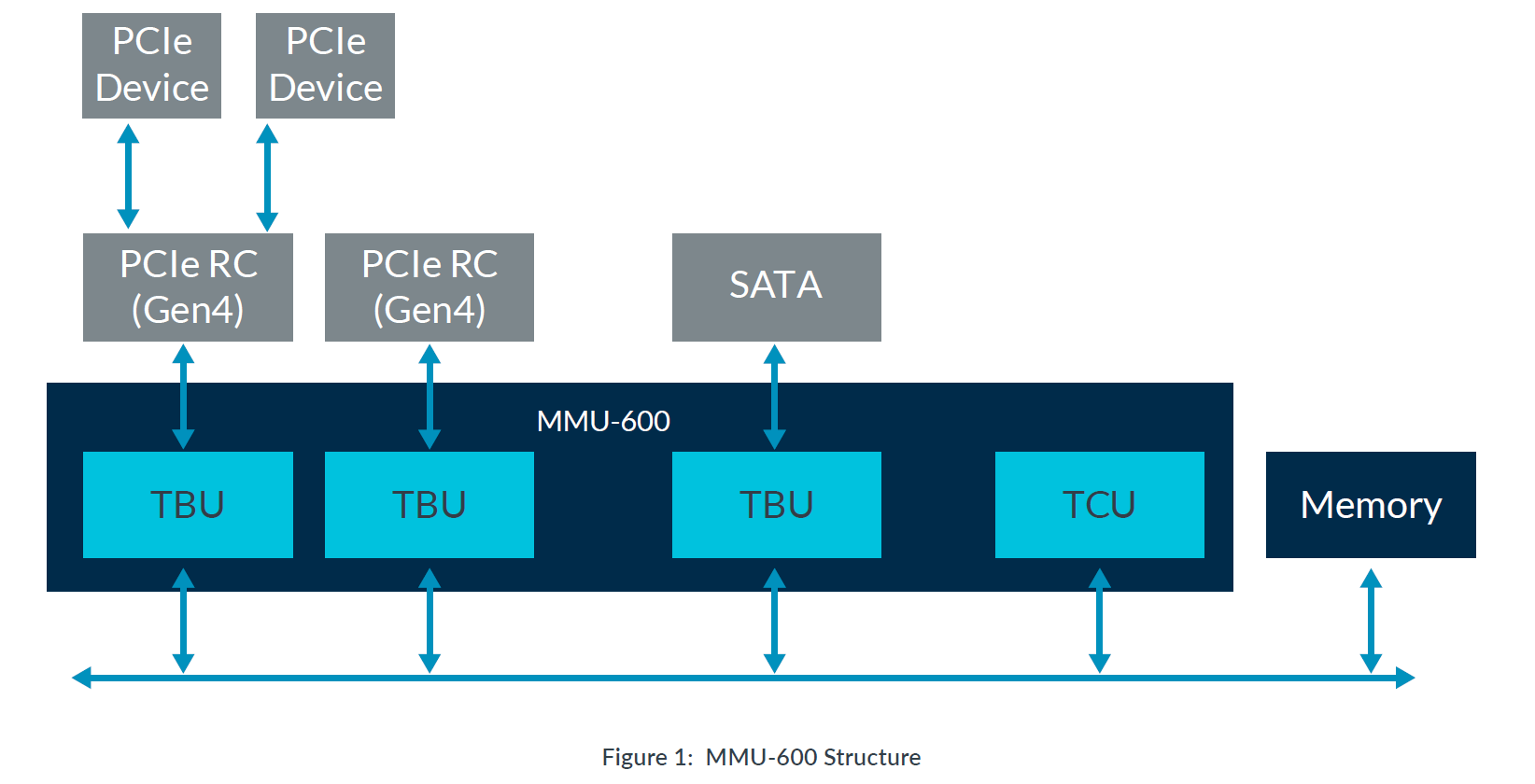

过去的十几年里,虚拟化被用来提高系统硬件利用率,减少运营成本,提高安全性。虚拟化技术使多个操作系可以独立运行于单个计算机系统实...

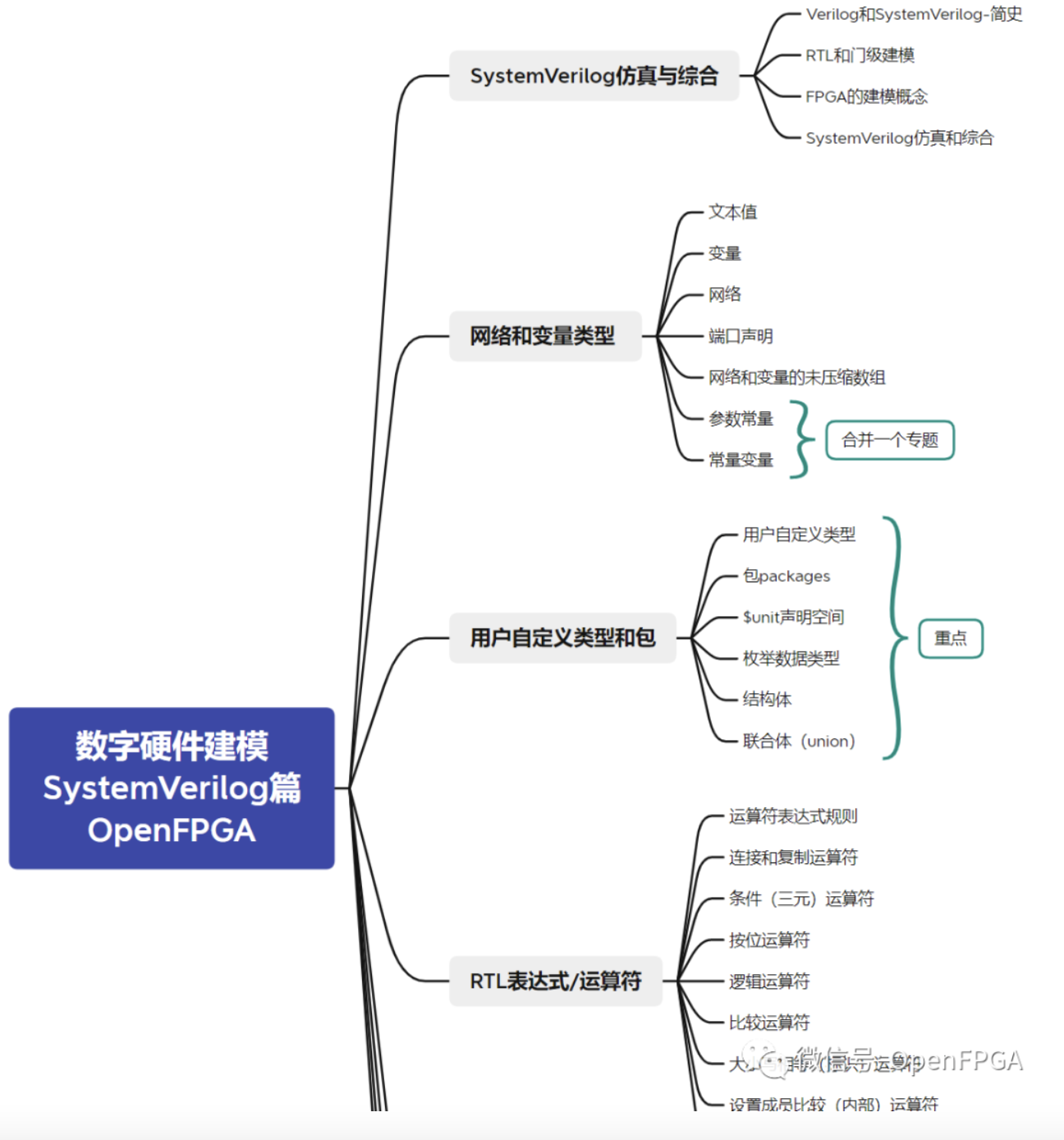

数字硬件建模SystemVerilog-归约运算符(Reduction operators)经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就...

经常使用RTL例如verilog进行数字逻辑设计的朋友,仿真一定是一个绕不开的话题。在一些标准的数字接口和协议上,使用仿真软件例如modelsi...

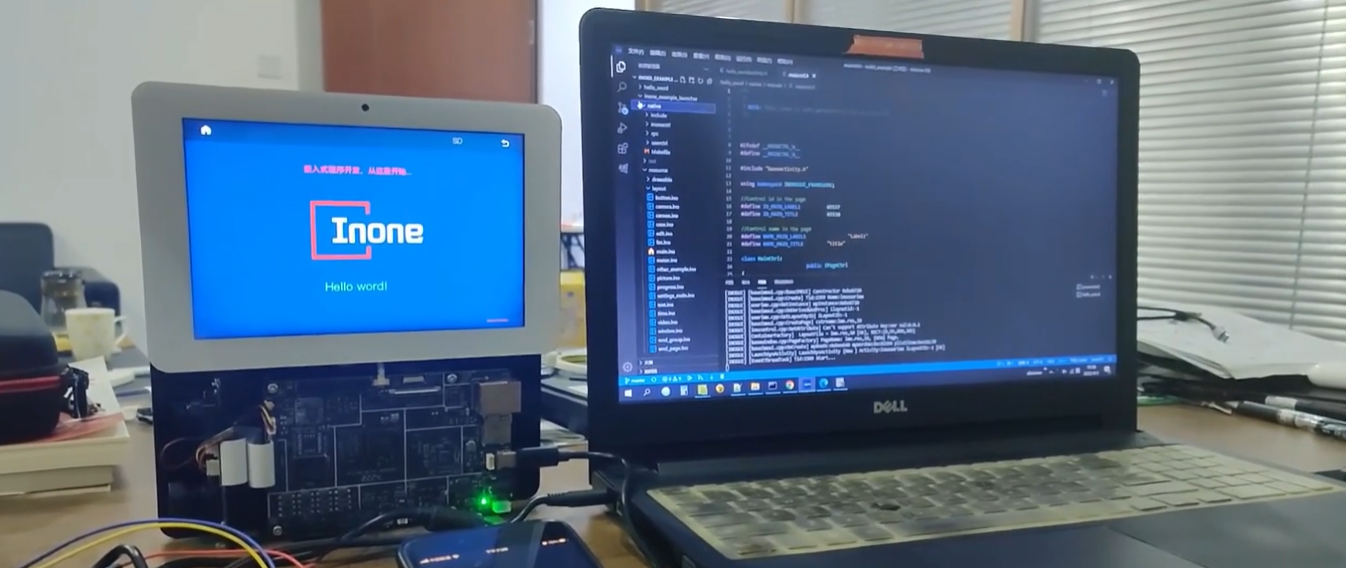

上回在V853开发板上体验了摄像头与UI的叠加效果,一键实现了V853开发板摄像头自由,该项目参考了INONE-EXAMPLE-8D例程里的项目源码,相...

正如我们所知,“bit”是无符号的,而“byte”是有符号的。那么,你认为下面两个声明是等价的吗? {代码...} 答案是不等价,因为: {代码...}...

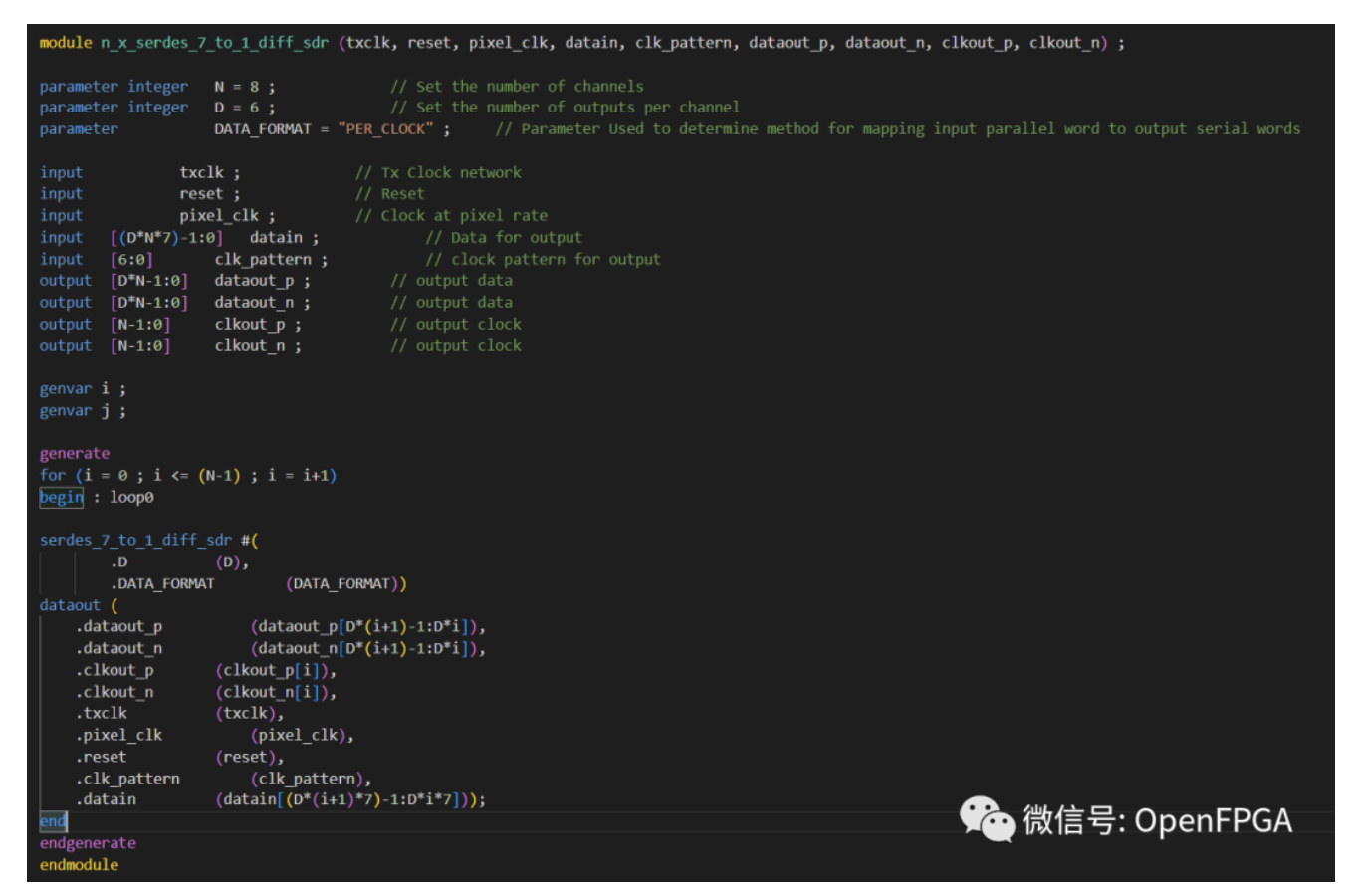

在使用xilinx官方例程《XAPP585》实现CameraLink接口发送或者接收数据时,有个程序还是值得学习的,下面把这段程序截出来:

利用这块屏,我们可以做很多事:起床时查看睡眠质量,室内健身或户外跑步时同时启动运动监测,随时查看心率等运动数值,中午定时叫醒午...

当别家千方百计让耳机变得更轻便、易携带时,它却做了个沉甸甸的大块头; 当别家还沉浸在月影黑、冰霜银、陶瓷白雅致风时,它却做了个五...

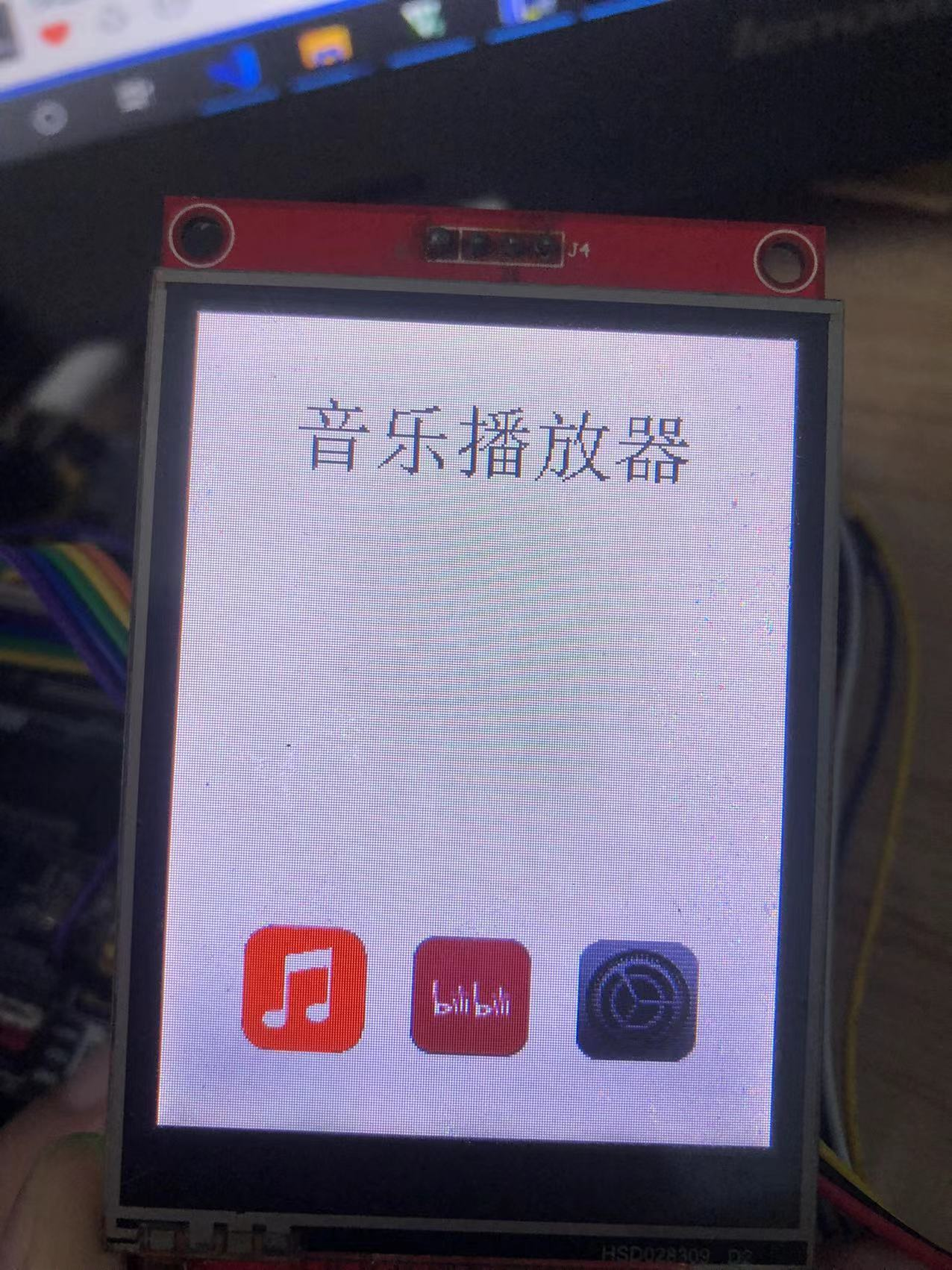

在上两篇文章实现了屏幕显示、触摸和DAC播放音乐的功能,趁周末抽点时间,又编写了从SD卡读取音频文件和界面的...

在完成所有项目后会开源,目前初步是想做一个通过DHT11采集信息,OLED显示,ESP8266上传,可通过小程序查看的简易智能家居事例。

Verilog始于20世纪80年代初,是一家名为Gateway Design Automation的公司的专有硬件描述语言(HDL)。最初的Verilog HDL的主要作者是Phi...

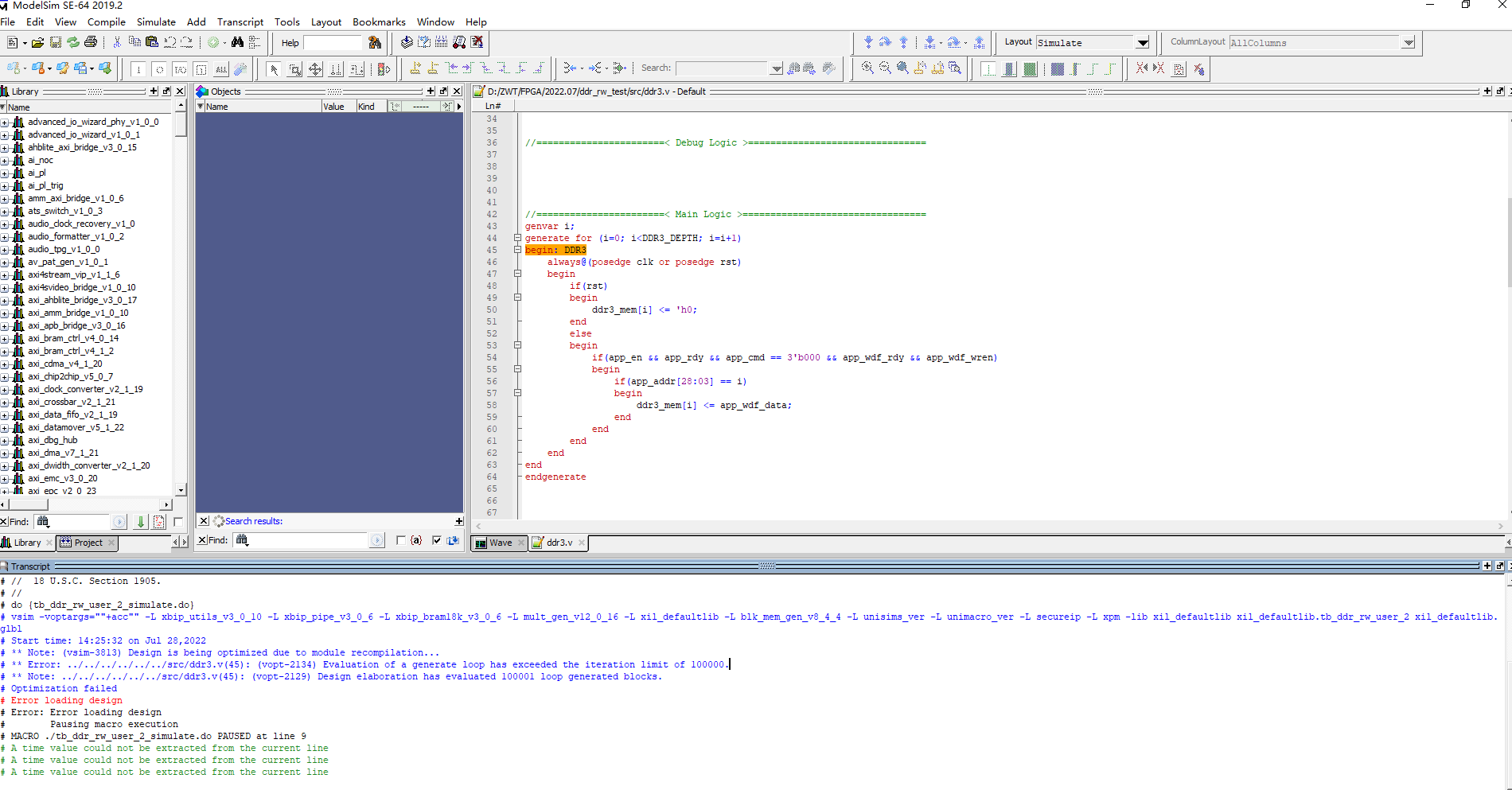

Generate for的用法:对于FPGA工程师来讲verilog语法可以说是不能再熟悉了,在verilog中generate for可以用来生成重复性的逻辑,比如下...

一家是除了车架、外壳、电池、小零配件外,可包揽一切的软硬件服务提供商华为;另一家则是细致入微的为自动驾驶提供单点服务的大疆。

自去年面市以来,AirTag 销量大幅上涨。据分析师郭明琪透露,2021 年 AirTag 出货量预估为 2000 万台,而到 2022 年这一数字有可能增至 ...

推荐一篇本团队近期发表的论文,一种用于智能网卡或DPU或可编程交换机的,支持P4语言的高性能开源解析器的设计。通信芯片也如CPU和DPU一...

想拥有自己的SystemVerilog IP库吗?设计时一个快捷键就能集成到自己的设计,酷炫的设计你也可以拥有!

1. 处理FPV中复杂度问题的两个简单办法作为FPV验证计划的一部分,我们应该尽考虑采取措施来减少FPV执行的DUT规模的 复杂度,当然如果设...

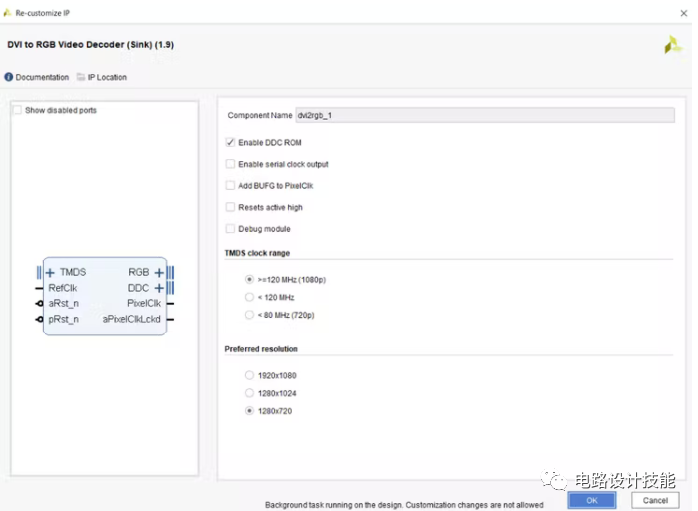

本文将介绍如何创建一个支持 HDMI 输入到输出的图像处理平台。这可以用作基于 HLS 的图像处理演示的基础。

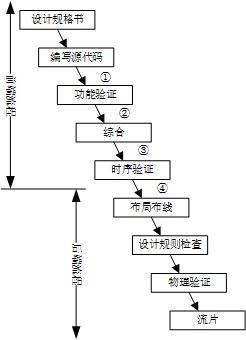

时序分析的基本步骤: 一个合理的时序约束可以分为以下步骤:时序约束整体的思路与之前我说的方法基本一致。整体的思路如下:先是约束时...

首先,如果你正在考虑使用FPV进行验证,你需要确保你的DUT确实适合使用FPV,例如控制逻辑或数据透传。

• 基于安谋科技STAR-MC1处理器的上海航芯ACM32芯片及方案介绍本文为基于安谋科技星辰“STAR-MC1”处理器的芯片公开课系列之上海航芯篇回顾...

使用插值算法实现图像缩放是数字图像处理算法中经常遇到的问题。我们经常会将某种尺寸的图像转换为其他尺寸的图像,如放大或者缩小图像...

SystemVerilog能够在许多不同的细节级别(称为“抽象级别”)对数字逻辑进行建模。抽象意味着缺乏细节。数字模型越抽象,它所代表的硬件的...

这几天,东航客机MU5735坠毁事故牵动人心。目前当务之急除了全力搜救,还要查明事故原因,而查明事故真相关键在黑匣子。希望能尽快找到...

学过一门计算机系统结构相关的课(微电子专业),上过这课的同学应该都“深(yi)有(yan)体(nan)会(jin)”。我一直认为学习新事物需...

要想深入理解Verilog就必须正视Verilog语言同时具备硬件特性和软件特性。在当下的教学过程中,教师和教材都过于强调Verilog语言的硬件特...

在每年找工作的时候,在校学生就会分割成软件岗位和硬件岗位两大阵营。心仪软件岗位的同学就是专注于各种算法和语法宝典;而立志硬件岗...

2014年3月,我曾经写过一篇文章:为什么不推荐为了找工作而学习FPGA里面讨论为什么我不建议一个没有基础的学生为了找工作而选择去学习FP...