GCC 13 编译器现已发布,并为大家带来了一些好东西。Arm 工程师和 GCC 社区为发布这一版本付出了艰辛的努力,本博客将介绍 GCC 13 中值...

2024年4月28日至2024年5月7日,极术社区联合安谋科技学堂组织了【五一赠书】免费赠送80本《Arm Helium技术指南》,掌握Cortex-M处理器DS...

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资...

2024年的北京车展,估计很多人都看周鸿祎的首日秀,很多人都追着雷军跑,回头一想,北京车展到底看了什么?有那么一种感觉,汽车行业有...

如今,嵌入式、物联网 (IoT) 和边缘机器学习 (ML) 应用广泛基于 Arm 平台运行。目前有超过 45 家芯片供应商提供 10,000 多种基于 Arm Co...

Bus Master Enable位于command寄存器的bit2,用于控制Memory and I/O Read/Write Requests。

本文和大家一起解密上汽荣威RX5 MAX版域控制器的设计方案。本方案的Tier1是上汽与TTTech的合资公司创时智驾。荣威RX5 MAX拥有3个毫米波...

2024-05-06 周一 17:20 开播 回顾中

2024-05-06 周一 17:00 开播 回顾中

2024-05-06 周一 17:00 开播 回顾中

在不断发展的 IT 基础设施领域,从广阔的云网络到资源有限的边缘环境,企业在各种基础设施部署中部署应用程序时会遇到无数挑战。每种部...

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资...

目录 1.车规MCU少见TrustZone什么是TrustZone2.1 TrustZone隔离了什么?2.2 处理器寄存器和异常处理2.3 如何切换安全状态2.4 TrustZone...

INVS默认使用了BPG,但是基于SDC理论下PG(path group)也是天然存在,两者在数据库里边有各自存在的方式,也可以共融共生中,通过其中...

引言在现代工业自动化和汽车电子领域,CAN总线以其高可靠性和实时性成为通信的主流选择。而CANopen协议,作为CAN总线上的一种上层通信协...

新能源汽车市场正迸发出巨大的活力,传统主机厂和新势力都纷纷推出各种车型,打起了价格战,各种新技术让人眼花缭乱。当前,战场硝烟弥...

在2023年11月的广州车展上,比亚迪的高端品牌仰望展示了一款创新概念车,其设计灵感来源于已发布的仰望U8越野SUV。这款概念车特别之处在...

自去年ChatGPT发布以来,数据中心的芯片需求迎来了新一轮的上升周期。当中尤其以英伟达GPU的表现最为亮眼。与此同时,作为芯片最终买家...

今天小编给大家带来的是国外Maker David Packman 的基于树莓派机器人-MBO,该机器人的外观设计灵感来自动漫Adventure Time中的机器人MBO...

TSN的目标是为工业自动化、智能交通、机器人控制等领域提供高性能、可靠性和实时性的通信。通过引入时间同步、流量调度和优先级控制等机...

✎ 编 者 按 最近收集一些代码覆盖率,其中牵涉到关于mem中streamReadSync的使用,在覆盖率收集过程中留意到其中具备的一些不可达的状态。

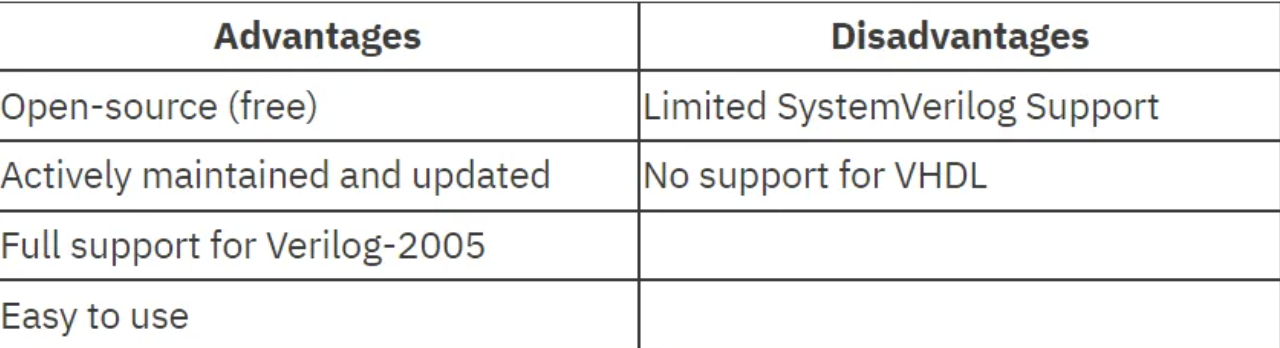

对于那些刚开始使用 HDL(如 VHDL 和 Verilog)进行编程的人来说,运行仿真以更好地了解该语言的工作原理非常重要。我们来看看四个仿真...

OFA的会议资料,我曾经在公众号上发过2次: 《RDMA、HPC资料分享:2019 OpenFabrics Alliance会议》 《OpenFabrics Alliance Workshop会...

导读:极术社区推出极术通讯,引入行业媒体和技术社区、咨询机构优质内容,定期分享产业技术趋势与市场应用热点。

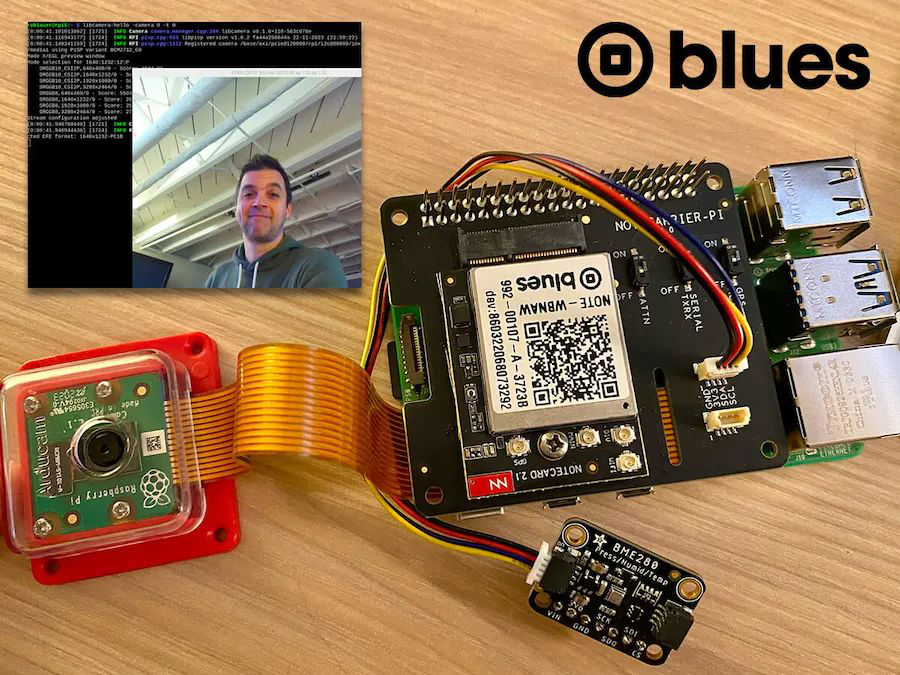

今天小编给大家带来的是来自美国的Maker Rob Lauer的基于树莓派5的蜂窝网络项目,了解如何为新的 Raspberry Pi 5 单板计算机添加低带宽...

大家好,我是痞子衡,是正经搞技术的痞子。今天痞子衡给大家介绍的是从功耗测试角度了解i.MXRTxxx系列片内SRAM分区电源控制。

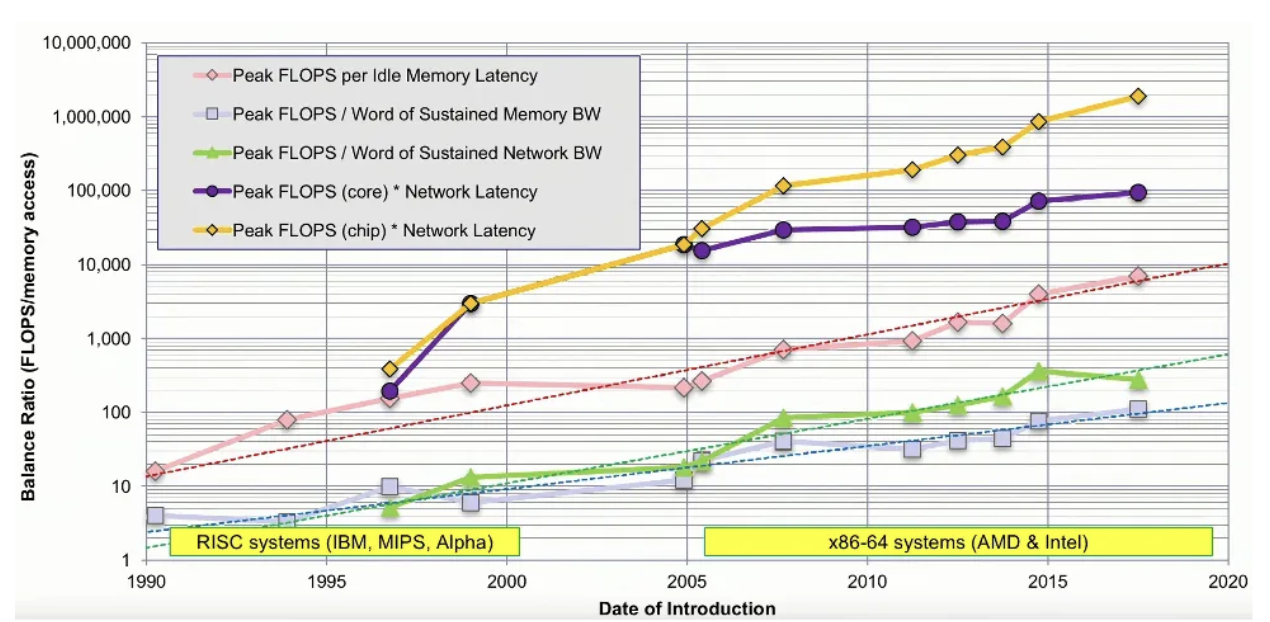

SoC 需要处理的数据量激增,虽然处理核心本身可以处理这些数据,但内存和通信带宽成为瓶颈。现在的问题是可以采取什么措施解决这个问题。

4月25日,芯驰科技在北京国际汽车展览会上召开2024春季发布会,重磅发布新一代中央处理器和区域控制器车规芯片产品家族。北京市经开区工...

内存分区和监控(MPAM)Arm 架构补充允许使用 PARTID 标识符对内存资源(MPAM MSC)进行分区。这允许操作系统和管理程序等特权软件在硬...

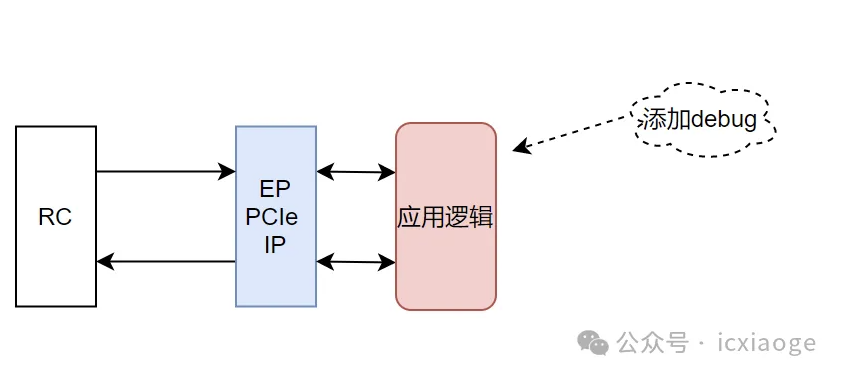

图1:debug设计添加位置图2:ltssm状态切换图pcie_ltssm作为PCIe链路训练状态机的实时状态,能够有效显示当前链路的链路状态。一旦PCIe...