为了在仿真阶段能够模拟物理器件的延迟,进行结构模型建模,SystemVerilog/Verilog中提供了两种类型的延迟用以模拟信号经过模型时的传输延...

在直接映射cache中,当发生miss时,新请求的数据块只能映射到一条特定的cacheline。 在这种情况下,此cacheline的内容将替换为新的内存...

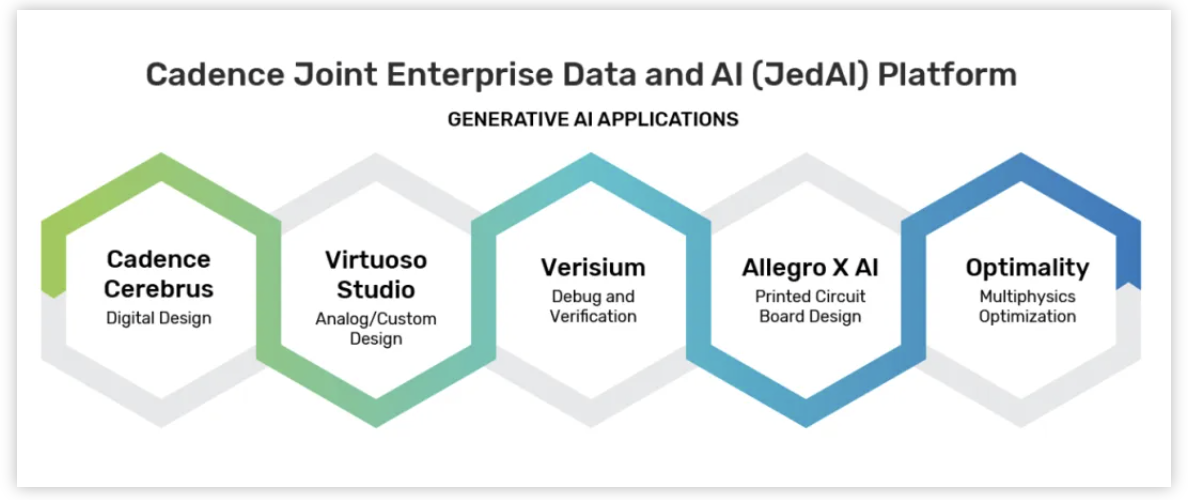

随着大模型的快速的发展,人工智能正在改变嵌入式硬件系统。在今年上海国际嵌入式展的开幕主题报告中,芯原股份董事长兼总裁戴伟民博士...

记录个在写SystemVerilog随机约束时遇到的一个小坑,如果没有认真去查看随机结果是否符合预期,还真不容易发现。

目录- Quad Rank相对Dual Rank MRDIMM的性能优势- TFF 2U高度内存尺寸改进散热密度- MRDIMM功耗接近翻倍:RCD & DQ Buffers影响较大- MR...

Interface Class是在SystemVerilog 2012版本中引入的,但目前在验证中几乎很少采用,大多数验证工程师要么不知道它,要么没有看到使用它...

DFI 协议中的写传输(Write Transaction)定义为 MC 通过 DFI 总线向 PHY 写入数据的过程,PHY 随后负责将数据转换为 DRAM 总线形式,发...

我们知道 LPDDR4 相比 DDR4 一项重要的改动是在单个颗粒上支持独立的双通道(Channel),单个通道位宽 16 比特。这样一来,系统可以在 D...

针对芯片设计中 DDR 控制器-PHY 集成相关问题,与芯片 DDR 相关硅前硅后奇怪问题 Debug,开设咨询窗口。如果你有相关问题,或者 debug ...

在介绍CLAHE算法之前必须要先提一下直方图均衡化,直方图均衡化算法是一种常见的图像增强算法,可以让像素的亮度分配的更加均匀从而获得...

在芯片设计中,SDF(Standard Delay Format)文件是一种关键的技术文件,它对于确保芯片设计的时序准确性和性能优化至关重要。以下是对S...

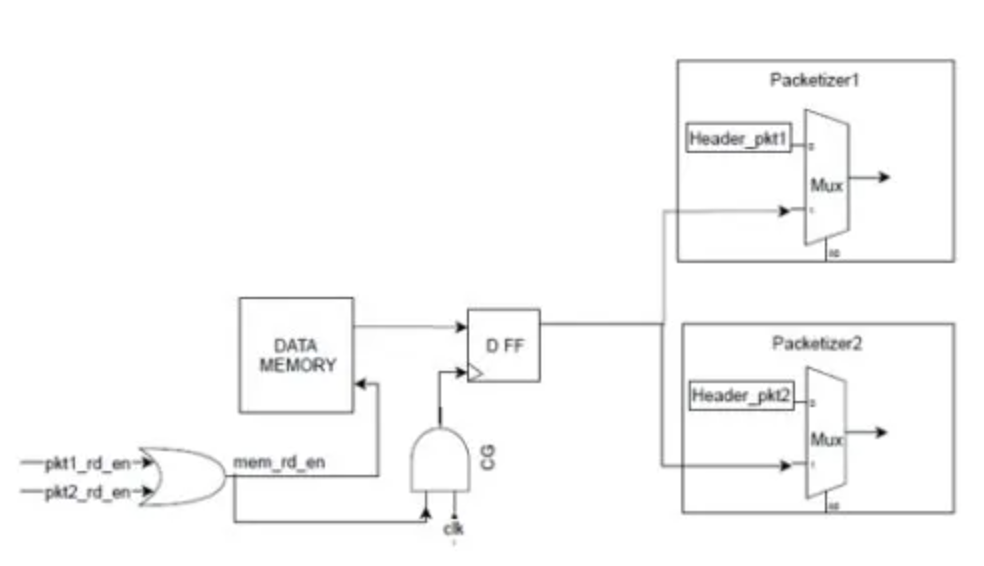

对于前端设计人员,经常会需要一个MUX来对工作模式,数据路径进行明确(explicit)的声明,这个对于中后端工程师下约束也很重要。这里介...

首先一切脱离研究方向谈论岗位本身都属于耍流氓(这里只讨论数字逻辑为主体的ASIC,模拟或者混合电路暂不讨论)。

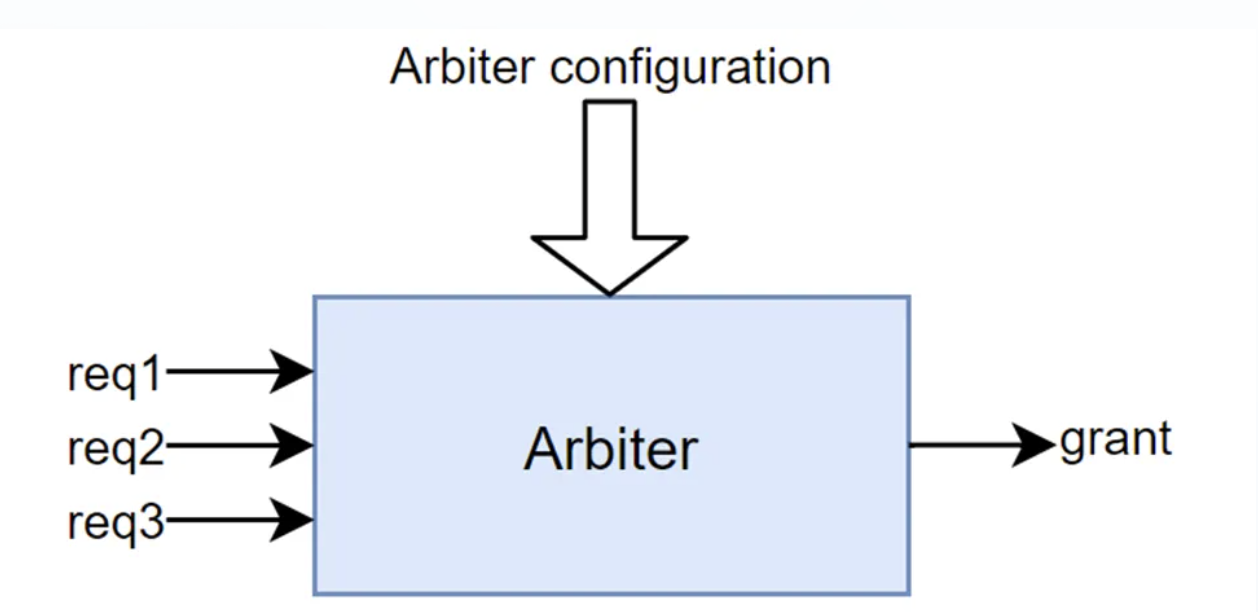

做SOC最典型的一项工作就是集成,也就是我们常说的连连看,看起来很简单,其实也很“简单”。前提是必须有集成工具,顶层下面的子模块之间...

传说这个世界上只有代码三种编辑器,Vim , Emacs 和其他编辑器,其中Vim被称作编辑器之神,Emacs被称为神的编辑器,当然,其他编辑器永...

策略模式是一种行为设计模式, 它能让你定义一系列算法, 并将每种算法分别放入独立的类中, 以使算法的对象能够相互替换。

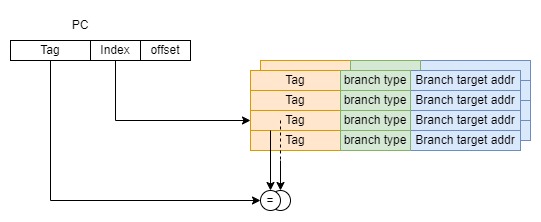

现代CPU须在指令预取pipeline stage具备性能良好的分支预测器,以给pipeline后端供应充足有效的指令。大多数CPU会使用 BTB(Branch Targ...

有人认为我验证做得很牛,也有人认为我的验证早就丢下了;有人认为我发现了各个项目的不少问题,也有人认为我在CMM库的几百个问题单大部...

随着这几年AI应用和AI芯片的发展,AI已经成为市场的的热点,各个芯片公司均逐步推出具备特色的AI芯片以对市场进行争夺。当前的AI芯片快...

在基于RTL的芯片研发流程中,我们对于RTL开发时的功耗优化投入了大量精力,但这只是可以节省的功耗的一小部分。该行业转向更大算力系统...

随着各种消费类设备智能化的巨大增长,这些应用正变得更加以数据为中心data-centric和计算密集型computation intensive。从IC设计的角度...

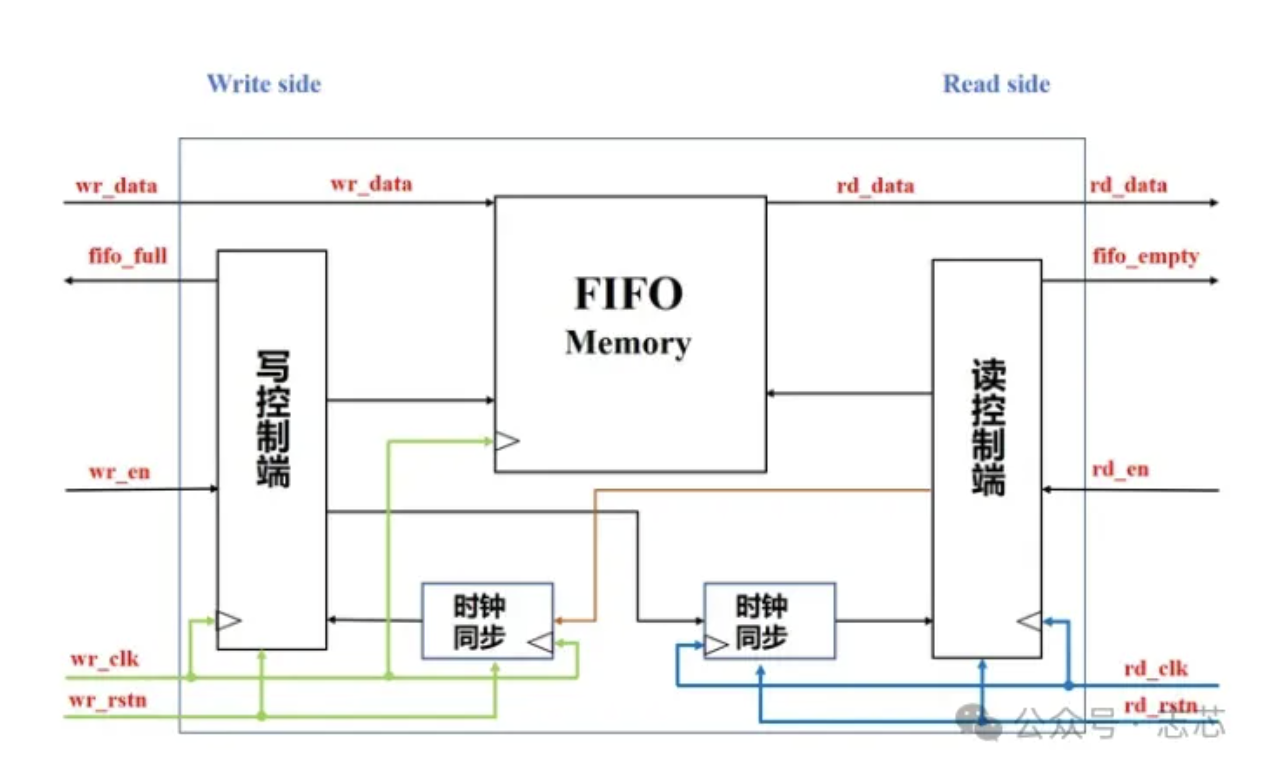

使用异步FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法。在异步FIFO中,读指针在读时钟域,写指针在写时钟域,所以不能...

2024年3月初,在美国硅谷举办的DVCon2024上,IEEE-SA和Accellera联合宣布通过IEEE Get Program可以免费获取IEEE 1800-2023 SystemVerilo...

Systemverilog支持集合操作符inside,有时合理使用inside操作,可以使得编码更为高效和简洁。inside操作符可以方便的比较一个数值、多个...

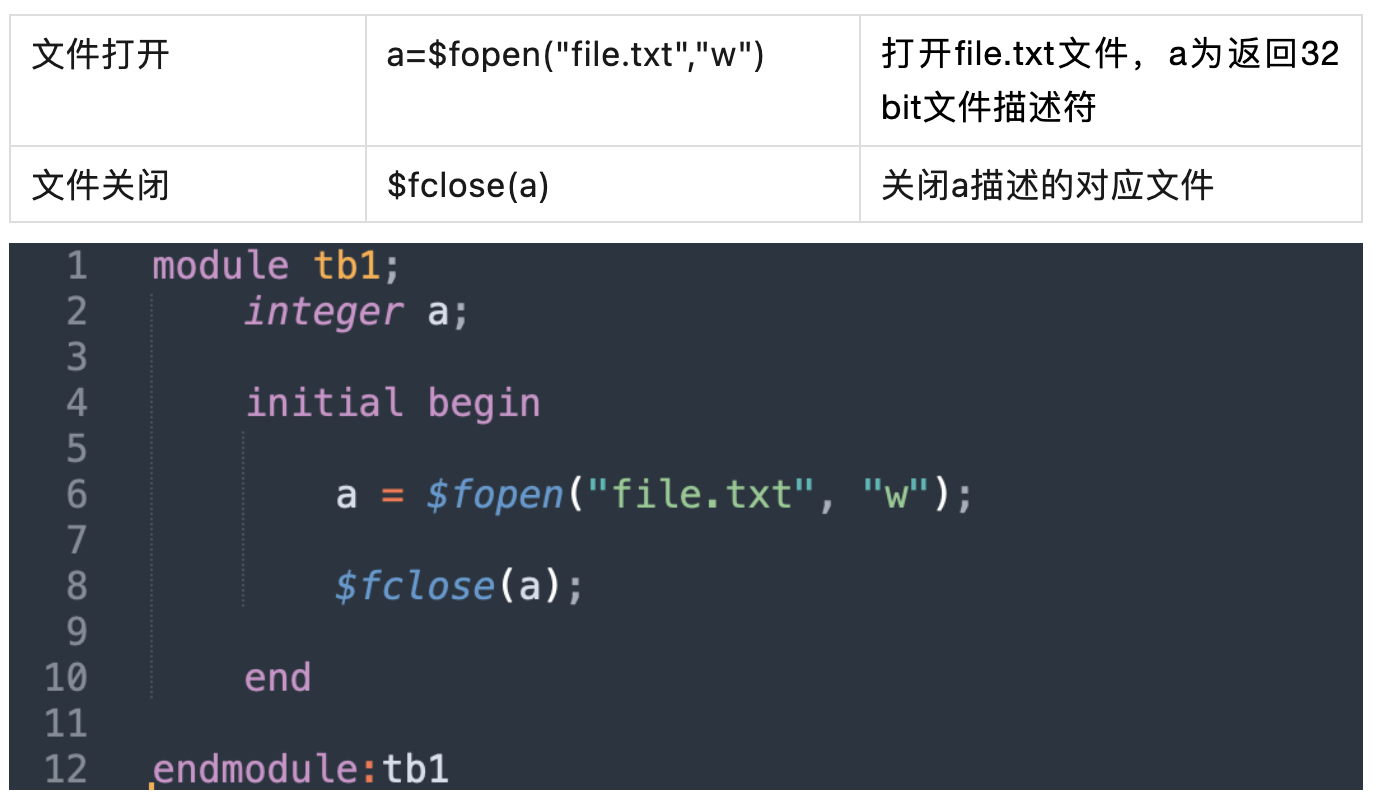

Verilog提供了很多对文件操作的系统任务和函数,例如打开关闭文件、向文件写入值、从文件读出值等等。

我们在编写一些比较复杂的Verilog代码时,通常需要进行大量的手动连线工作,这种工作十分容易出错,并且在代码模块的嵌套层级较多时,更...

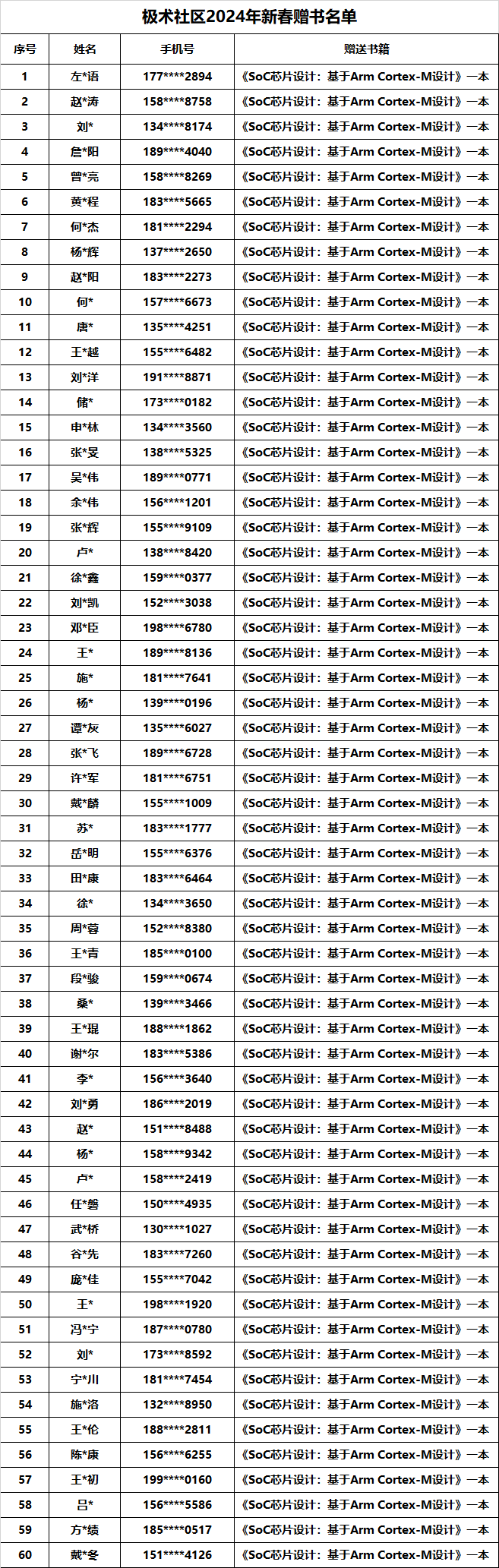

2024年1月26日至2024年1月30日,极术社区联合安谋科技学堂组织了【新春赠书】60本《SoC芯片设计:基于Arm Cortex-M设计》免费送,全面掌...

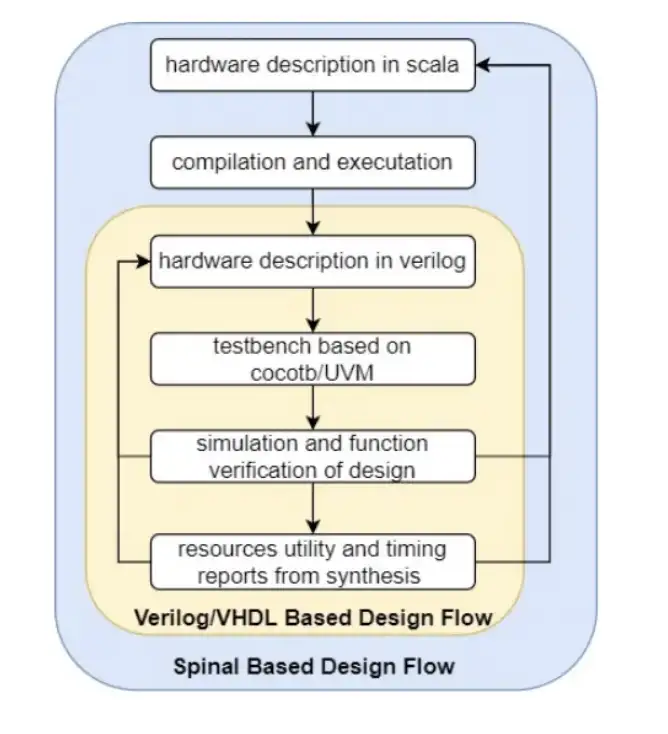

摘要:领域特定架构已成为计算机发展的一种趋势。在提供更高效算力的同时,它也给底层硬件的开发带来了更大的挑战。传统的芯片设计和验...

UVM库是类的集合,它通过提供如何使用SystemVerilog中的功能结构,使SystemVerilog语言使用起来更为通用顺畅。然而,在许多情况下,UVM...