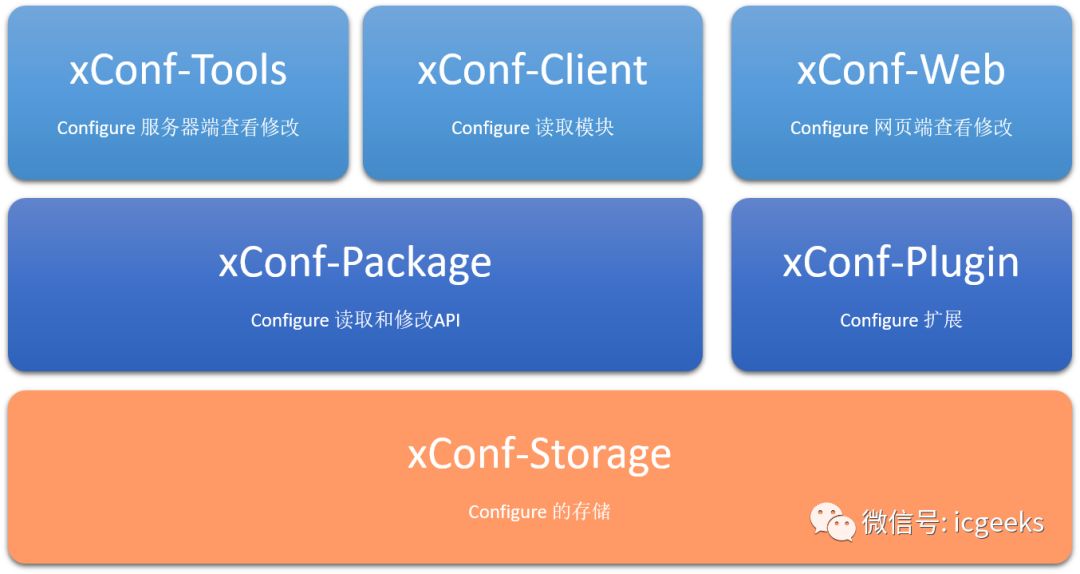

Alice 在IC 极客群里谈到了配置管理,那我也来谈一谈。配置的设计更多的是在软件的管理和使用中被提及,而IC 流程中,配置也是需要的,...

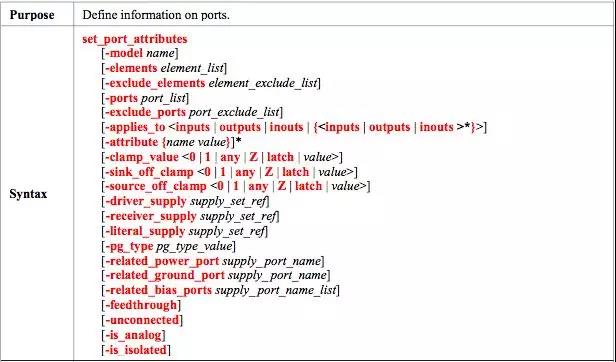

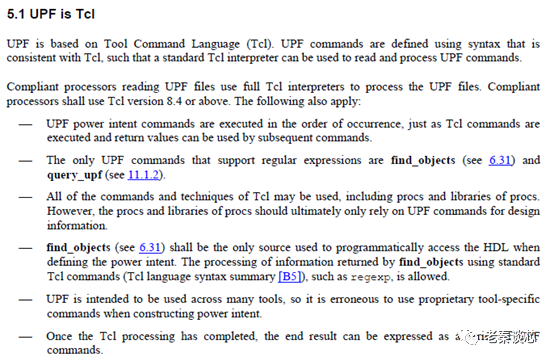

在很早之前写过一篇1801 Macro 如何建模的文章《万物皆有裂痕,那是光进来的地方:1801 Macro》,彼时年少,过于柔骚,技术文偏要按个如...

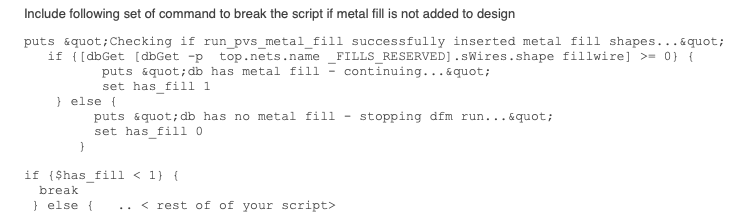

有驴友在后台问Innovus 的dbGet, 老驴是从Common UI 开始学习Innovus 的,所以并不熟悉dbGet, Common UI 的get\_db 也很好用。在support...

Jim Keller 毕业于宾西法尼亚州立大学,在那里获得了电子工程学士学位。与其他芯片领域大神常见的硕士和博士不同,Jim Keller一直就是学...

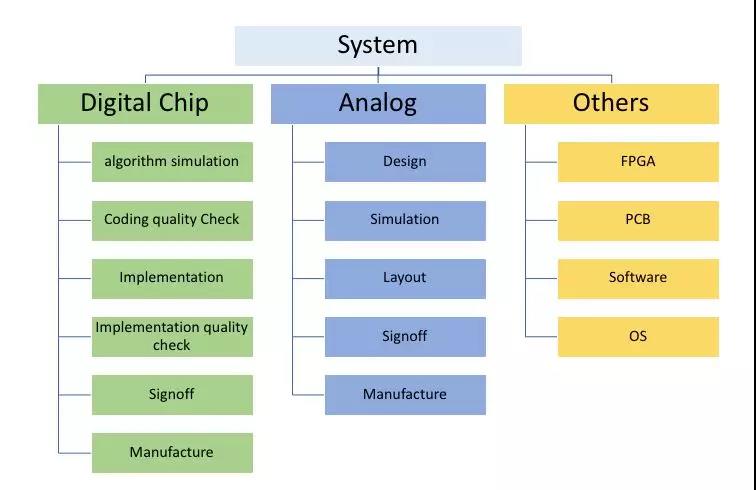

在各方助力下,集成电路成了时代热点,有大量文章在写芯片设计之复杂之困难,本文从EDA使用角度捋一遍芯片设计流程。

没人会记得什么时候ARM公司的各类“IP”已经进入到生活中各类平台中,手机(CPU)、电脑(EC、外围接口芯片)、路由器等等,而很多不了解...

最近看到一个优秀的个人网站,来自宝岛,网站签名就霸气十足——繼續用 Machine-learning 解放半導體產業競爭力 (Cost-effectiveness, Com...

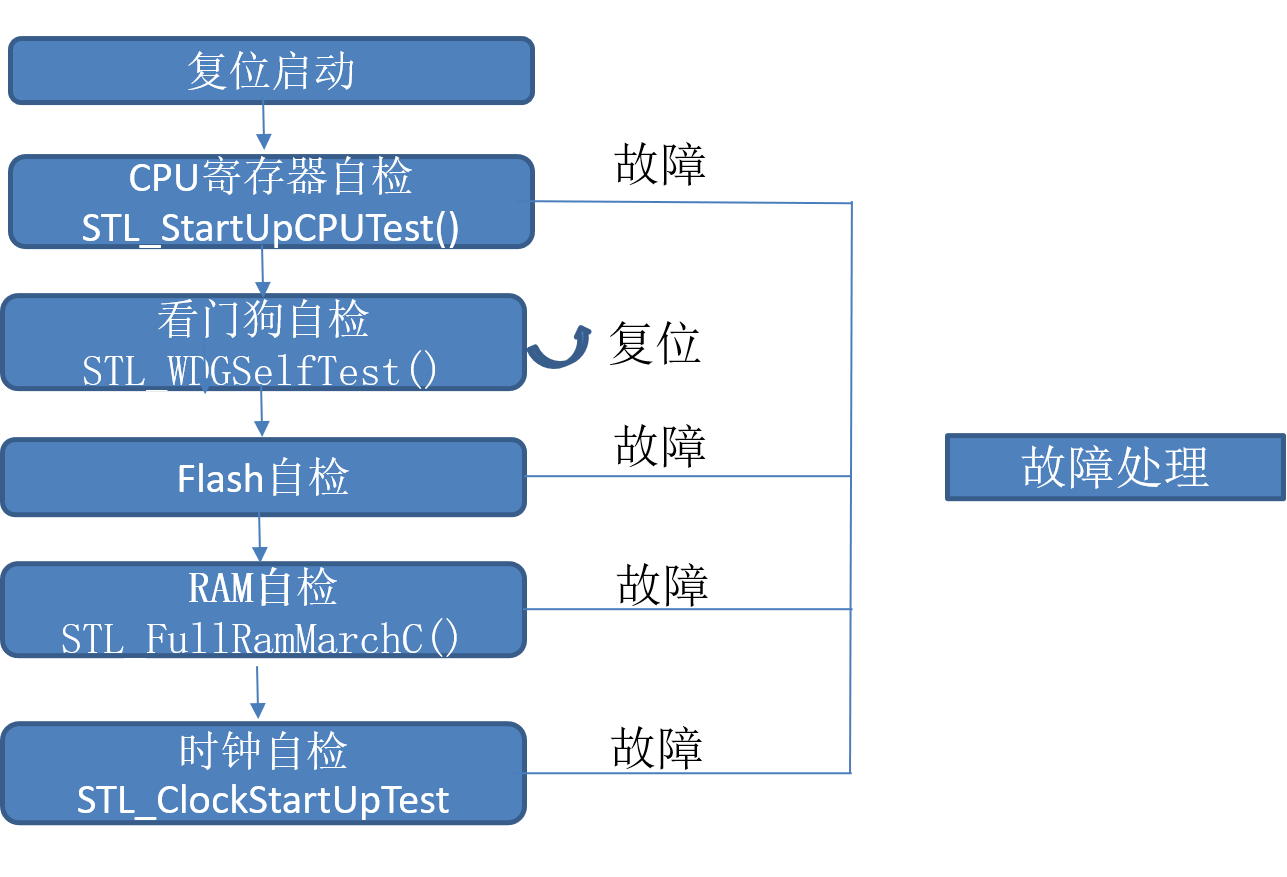

在前面的几个章节中我们介绍了关于MM32F0130系列的ClassB 认证的实现方式,本章节中我们将为大家介绍在MM32F0130上ClassB认证的各部分代...

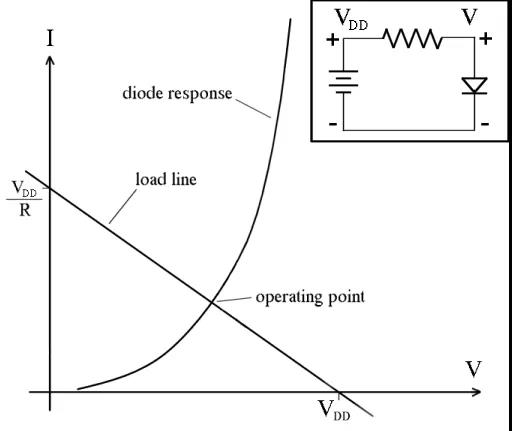

以下图为例,该电路的解或者工作点即负载线与diode IV 曲线的交点,其中负载线电流方程为Diode 电流方程为在工作点处,因为diode的方程是一...

当2020年10月份,NVIDIA在其GTC 2020大会上大张旗鼓的宣传DPU之后,整个行业热了起来,大家都在问:什么是DPU?DPU到底能干什么?DPU和G...

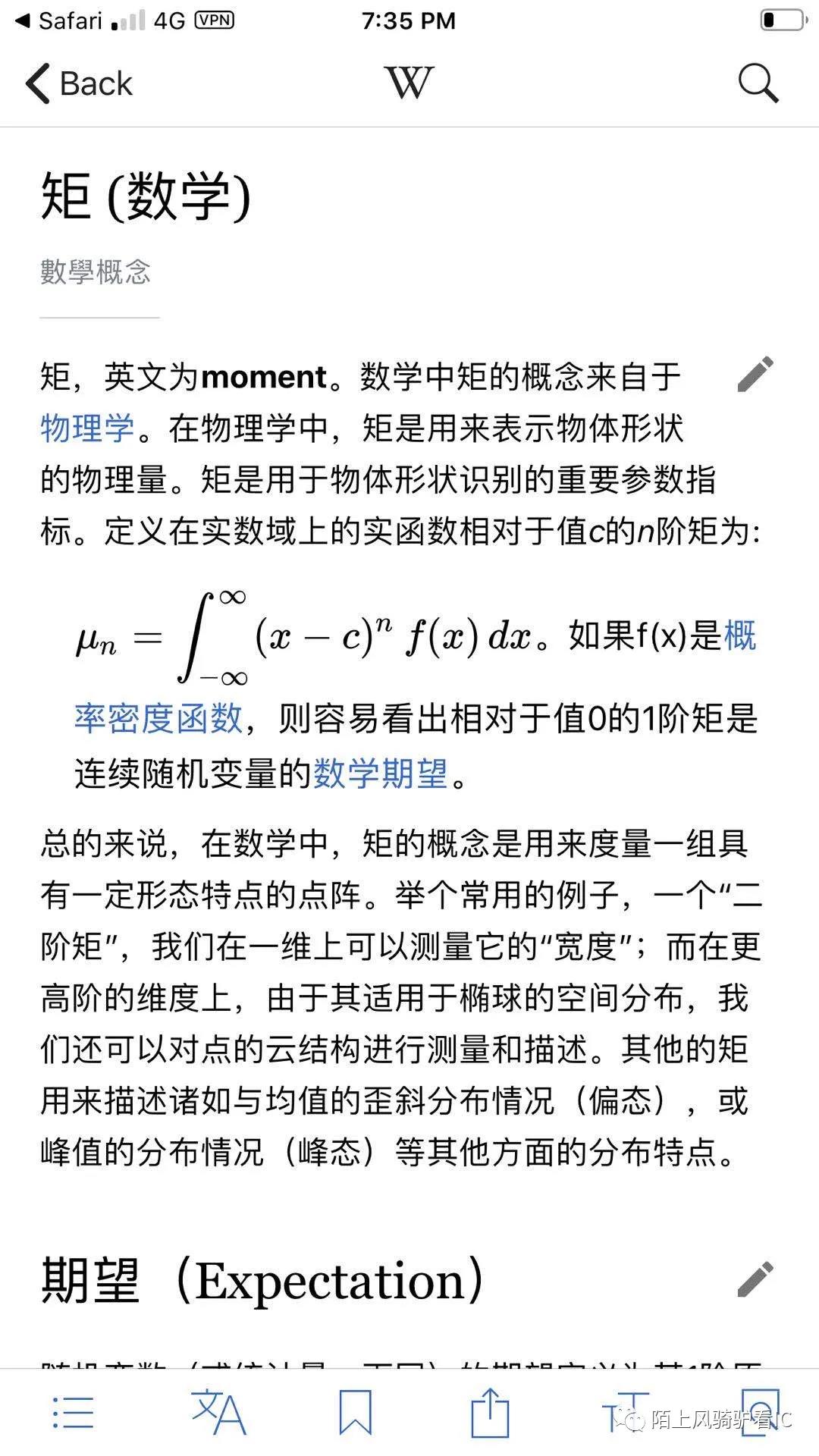

群里大牛们从讨论moment based LVF 追溯到数学中的矩,还找到了一篇知乎大牛深入浅出的回答,奇文共欣赏!

简而言之,bugs 可以从简单的拼写错误到复杂的逻辑场景(scenarios)。此外,bugs 的严重程度可以从无伤大雅到导致项目灾难性地失败。

众所周知,用于FPGA开发的硬件描述语言(HDL)主要有两种:Verilog和VHDL,VHDL的出现时间要比Verilog早,Verilog由于其简单的语法,和C...

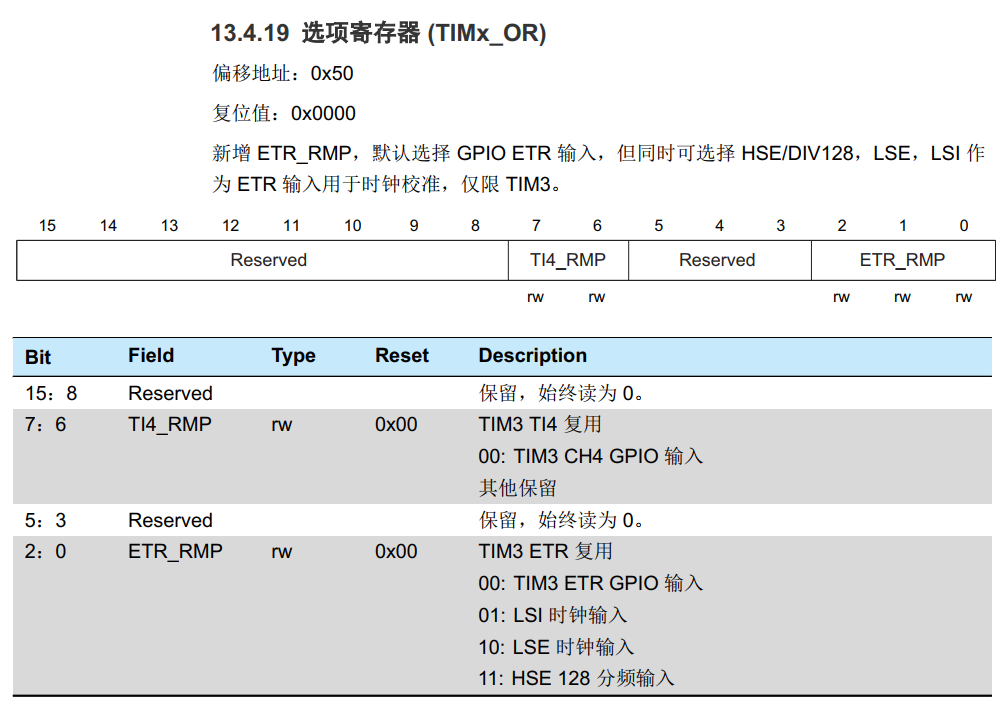

外部高速时钟源(HSE):外部晶振选择范围为2-24MHz外部低速时钟源(LSE):可以使用一个32.768KHz的晶体/陶瓷谐振器构成的振荡器产生内部高...

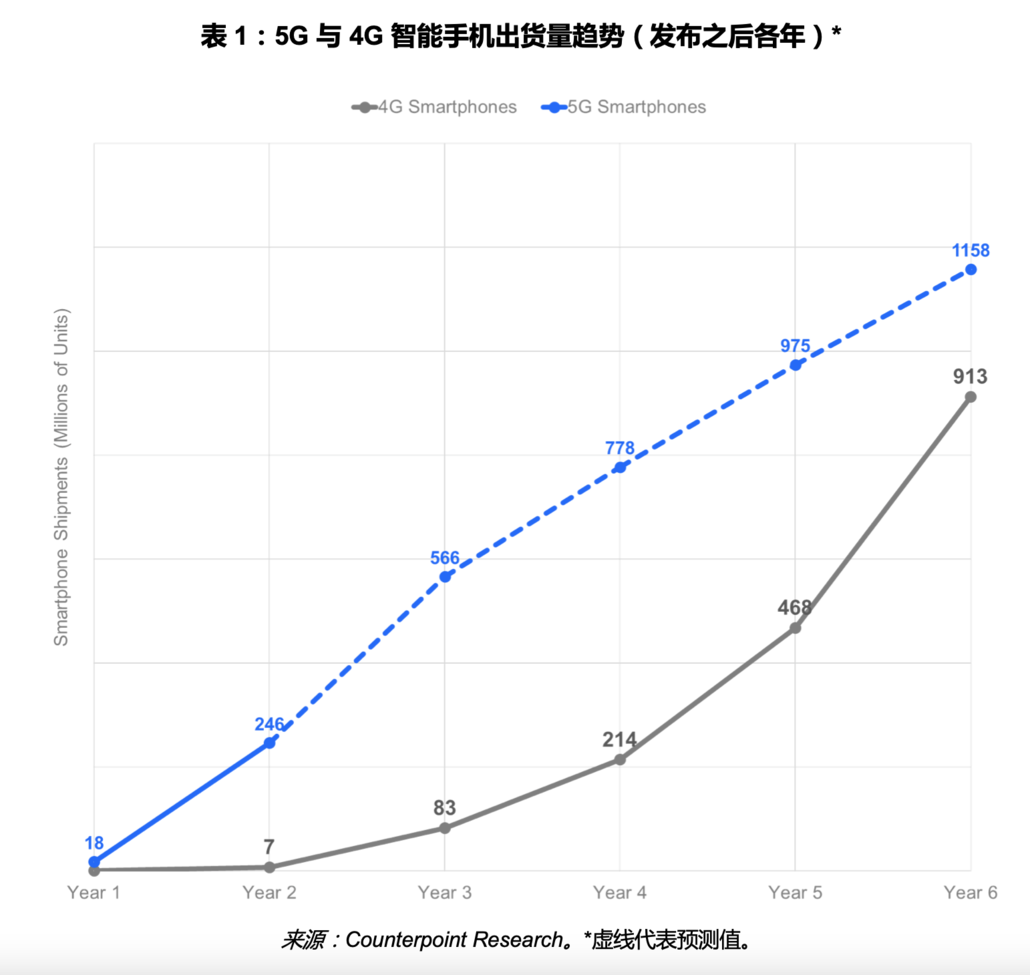

近日,全球成长最快智能手机品牌 realme 与 Counterpoint Research 合作发布了一份题为《5G 全球普及》的白皮书,探讨了全球 5G 智能手...

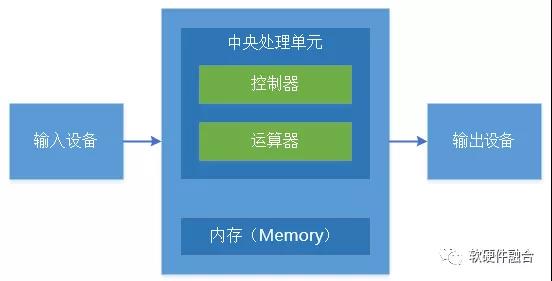

举个例子:cache,通过层次化的存储结构折中解决存储成本-大小-速度问题。寄存器离核最近,速度最快,但是成本也最大。其次是L1 cache、...

前面的文章里,讲了一些SoC低功耗相关的设计方法,比如多电压域和电源开关等,《SoC设计之功耗 -- Power Gating》,《SoC设计之功耗 -- ...

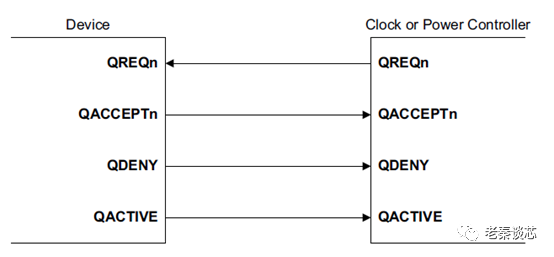

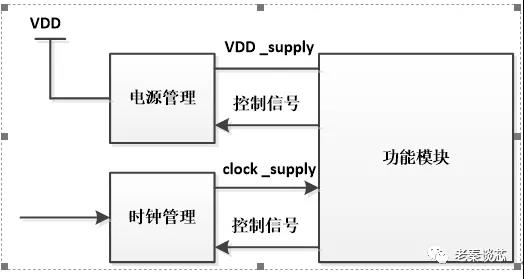

Q-channel是ARM公司定义的一个低功耗接口,是从AXI的低功耗接口演变过来的,其用处是控制设备静止(quiescent)状态时的时钟和电源。

开始前请大家回忆一下动态功耗的公式。工作电压和翻转频率会直接影响动态功耗值,那么是不是可以在这两个参数上做做文章来降低芯片功耗...

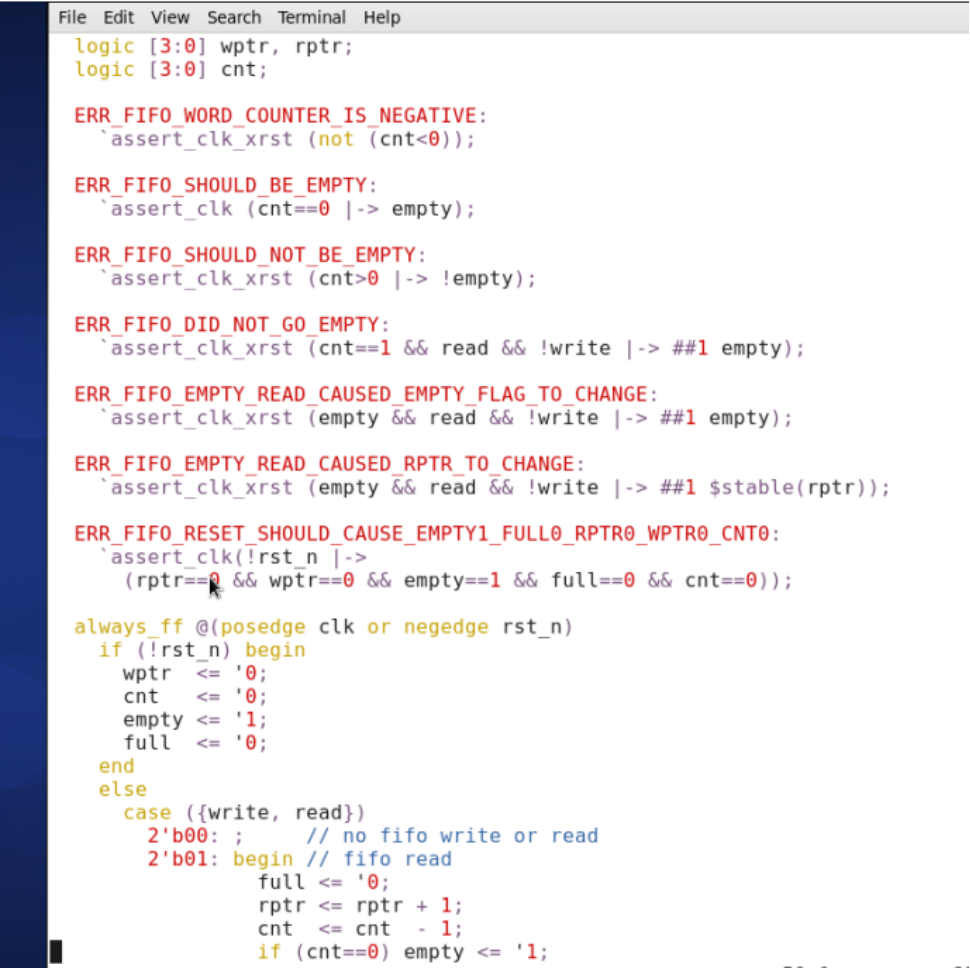

相比Verilog HLD,数字IC设计(RTL开发)人员会觉得SVA学习起来比较复杂。如果一个设计人员不得不书写超过3行的SVA代码,这个工作肯定会...

-Chiplet小芯片能否做成异构计算?-内存带宽跟不上PCIe:引出了串行化的OMI-低延时“近端内存”& “远端”CXL.mem内存共享-OCP HPC模块:OAI...

上周写IR drop的时候想起,当初写RTL功耗计算只写了原理性的东西,今天再写一些实操方面的吧,以PowerArtist软件为背景。

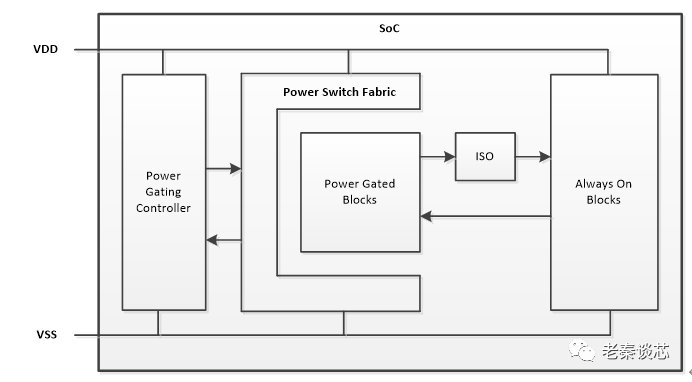

上期讲的多电压域设计主要还是解决的动态功耗问题,今天来看一种降低静态功耗的方法—电源门控(power gating)。当芯片内部的模块/IP不...

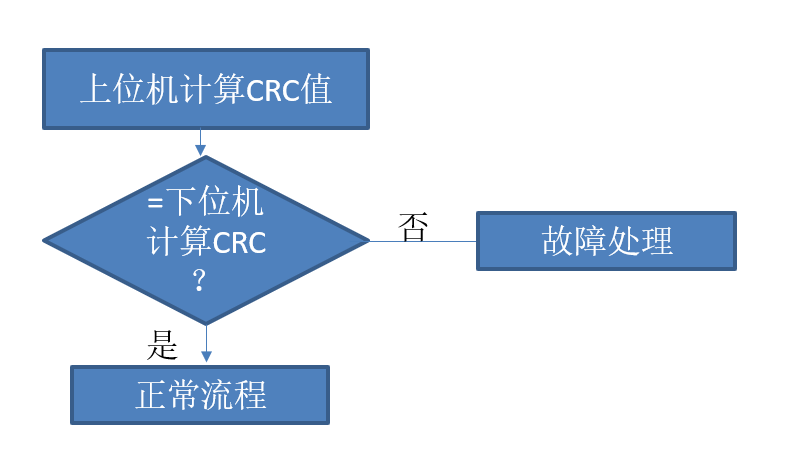

测试Flash存储器完整性时,需要用到CRC校验,在参考代码中我们使用了硬件的CRC单元,通过硬件CRC生成器完成的CRC计算大大降低CPU负载。

本周继续在电压上做文章,我们来看一看多电压域(multi-voltage domain)设计。毕竟SoC的动态功耗跟供电电压的平方成正比,降低一点供电...

书接上回,今天我们来聊一聊RTL级功耗计算的问题。上篇讲到有很多种低功耗设计方法,那么在项目中选择哪些来做呢?在抉择前如果有数据支...

没想到大家对IR drop这个话题很感兴趣,那就接着再多写一点,后面以redhawk软件为背景加以介绍(大A厂是不是考虑给我一点推广费啊,哈哈...

SoC电源/地网络给整个芯片供电,一个设计合理的电源/地网络要保证整个芯片的性能和可靠性。如果在电源/地网络上引入了噪声,可能导致电...

FPGA编译流程是指将一个FPGA设计从普通RTL描述转换为比特流所需要的一系列步骤。编译流程的顺序会有所不同,这取决于所使用的工具。然而...

今天来研究一个相对冷门的话题,电迁移(electromigration)。我们先来看一下,百度百科是如何定义的:电子迁移是上世纪50年代斯茂·斯迪...