【嘉德点评】武汉新芯发明的晶圆键合方法,通过在待补偿晶圆施加应力,在待键合的上晶圆和下晶圆上消除相对形变量差值,从而获得键合结...

基于FPGA的SOC在嵌入式系统应用越来越广了,往往一个复杂系统使用一个单芯片基于FPGA的SOC就搞定了。比较流行的方案主要有Altera/xilinx...

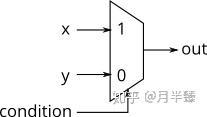

假设你正在设计一个电路来控制手机的振铃器和振动电机。当手机来电时(input ring),电路必须把震动( output motor = 1 )或响铃( outpu...

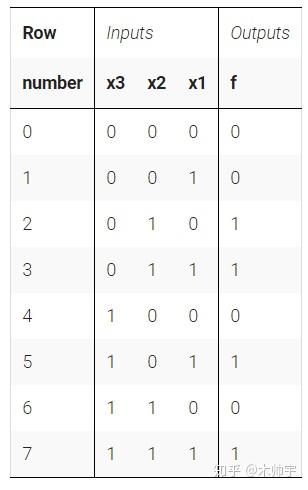

在前面的练习中,我们使用简单的逻辑门和多个逻辑门的组合。这些电路是组合电路的例子。组合意味着电路的输出只是其输入的函数(在数...

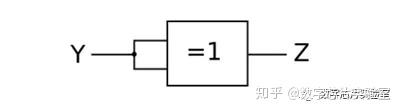

转载自:知乎首先附上传送门:[链接]Problem 45 NOR实现如下电路:解析: 一个或非门 {代码...} Problem 46 Another gate实现如下电路:...

集微网报道(文/无剑芯)近期,有机构预计,2020年,中国大陆厂商在全球AMOLED面板驱动芯片市场中的占比将达5%。该预测很可能过于乐观,...

设计电路来计算输入矢量中 ’1‘ 的个数,题目要求建立一个255bit输入的矢量来判断输入中 ’1‘ 的个数。

1、连续赋值和过程赋值之间有什么区别?2、initial和always中的赋值有什么区别?initial和always中的赋值都是过程赋值。3、阻塞和非阻塞...

集微网(文/Kelven)“华为海思在IPC SoC芯片市场已经一家独大,占据全球70%以上市场份额;在视频监控领域市占率也已经突破90%以上,几乎...

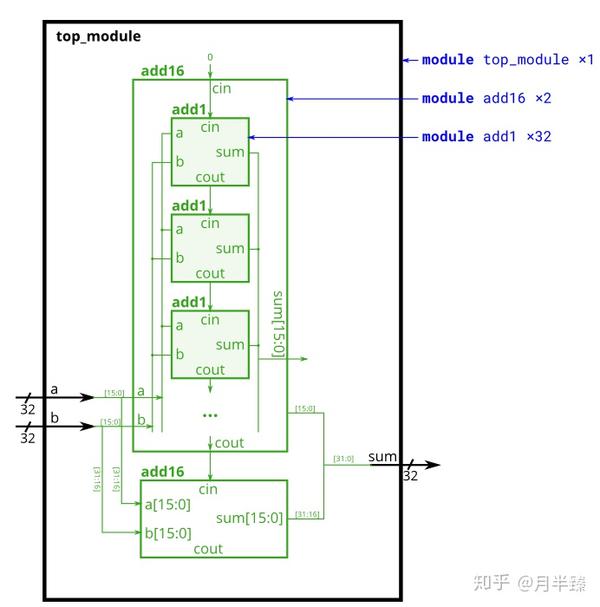

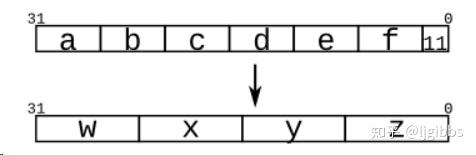

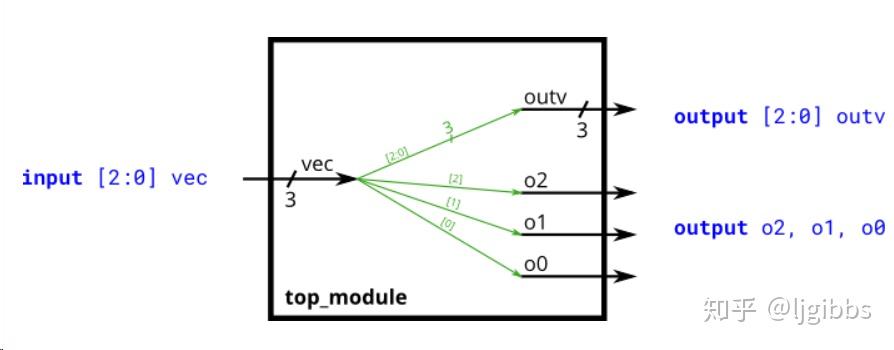

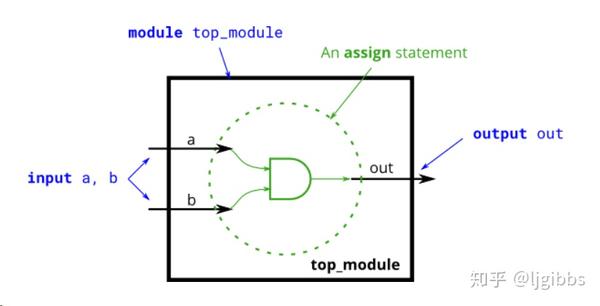

转载自:知乎本系列文章将和读者一起巡礼数字逻辑在线学习网站 HDLBits 的教程与习题,并附上解答和一些作者个人的理解,相信无论是想 7...

集微网消息(文/holly),2019年3月,国家发布了《超高清视频产业发展行动计划(2019年-2022年)》,该文件推测到2022年,4K产业生态体系...

转载自:知乎本系列文章将和读者一起巡礼数字逻辑在线学习网站 HDLBits 的教程与习题,并附上解答和一些作者个人的理解,相信无论是想 7...

转载自:知乎本系列文章将和读者一起巡礼数字逻辑在线学习网站 HDLBits 的教程与习题,并附上解答和一些作者个人的理解,相信无论是想 7...

转载自:知乎本系列文章将和读者一起巡礼数字逻辑在线学习网站 HDLBits 的教程与习题,并附上解答和一些作者个人的理解,相信无论是想 7...

转载自:知乎本系列文章将和读者一起巡礼数字逻辑在线学习网站 HDLBits 的教程与习题,并附上解答和一些作者个人的理解,相信无论是想 7...

在2020年的用户大会(SNUG)上,Synopsys介绍了一款新的数字前端工具RTL Architect, 虽然现场没有演讲提供使用体验,但是相信不少公司已经...

转载自:知乎本系列文章将和读者一起巡礼数字逻辑在线学习网站 HDLBits 的教程与习题,并附上解答和一些作者个人的理解,相信无论是想 7...

转载自:知乎本系列文章将和读者一起巡礼数字逻辑在线学习网站 HDLBits 的教程与习题,并附上解答和一些作者个人的理解,相信无论是想 7...

北京时间 9 月 16 日凌晨,苹果公司召开特别活动,推出了 Apple Watch Series 6 和 Apple Watch SE,并且为 Apple Watch 打造的首个健身...

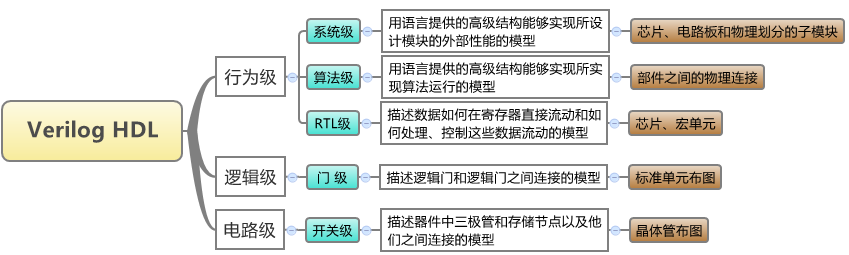

转载自:知乎本系列文章将向大家推荐一个学习 Verilog 的好去处:HDLBits. HDLBits 在提供 Verilog 基础语法教程的同时,还能够在线仿真...

转载自:知乎本系列文章将向大家推荐一个学习 Verilog 的好去处:HDLBits. HDLBits 在提供 Verilog 基础语法教程的同时,还能够在线仿真...

集微网(文/Kelven)时间的巨轮来到9月15日,宽限期已到,华为供应链正式遭遇断供。在今年5月15日和8月17日美国对华为实施第二轮与第三...

1、define宏的使用:define经常用来代替某些复杂的文本内容或数字,也可以用来构造字符串。``

1、generate用法定义genvar,作为generate中的循环变量;generate语句中定义的for语句,必须要有begin,为后续增加标签做准备;begin必...

即便是功能仿真相同的RTL代码,不同的代码风格也会得出不同的综合结果。我们不能仅仅依赖于综合工具来fix代码风格糟糕的设计!

下面是门控时钟(clock gating)的最简单实现方法(使用与门):从理论上讲,这是可行的:当使能信号Enable为高电平时,时钟将被传递到...

写此文时,时间临近国庆。中午的阳光还似盛夏,不过气温低了许多。路边插了很多红色的旗帜,超市的折扣让这几天更加喜庆。

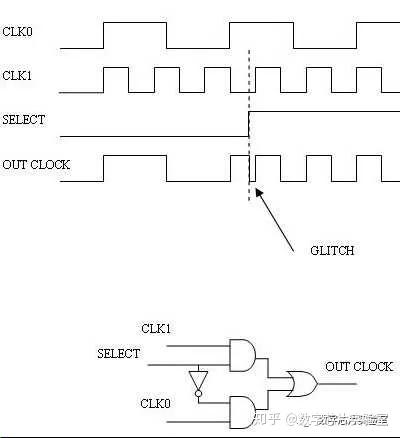

所复用的两个时钟频率可以完全无关,也可以是彼此的倍数。在任何一种情况下,都有可能在时钟切换时产生毛刺。时钟上的毛刺会造成整个系...

要获得一个高质量的Topographical synthesis结果,需要一个良好的physical start point。

门级仿真(Gate level simulation)是对综合后,已经完成映射(mapping )到工艺库的数字设计进行验证的方法。