本文你将了解到:现有芯片布局(floorplan )设计过程的痛点。 人工智能如何优化这一过程,将所需时间从数周缩短到数小时。 扩展相同方...

然而有个问题一直困扰着大家,开源硬件能挣钱吗?如果不能赚钱,有什么力量能持续输血让这个行业保持活力?

11 月 17 日,2022 骁龙峰会第二日,高通带来新款 AR 芯片平台骁龙 AR2。 一改以往 XR 平台系列的命名,直接将新平台唤作 AR。 在媒体连...

11 月 16 日,一年一度的骁龙峰会正式召开。主会场设在美国夏威夷,海南三亚再次成为会议的分会场,面向中国用户。

影像是全人类的旺盛需求,我们的生活被手机摄像头彻底改变了。极具活力的中国市场引领了手机摄像技术的发展。

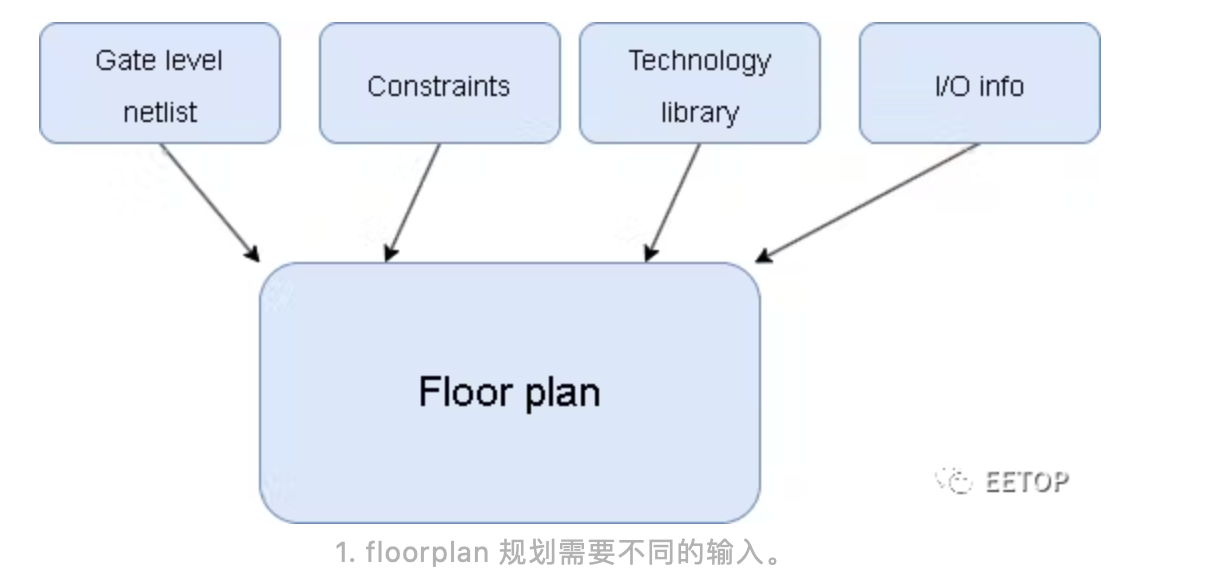

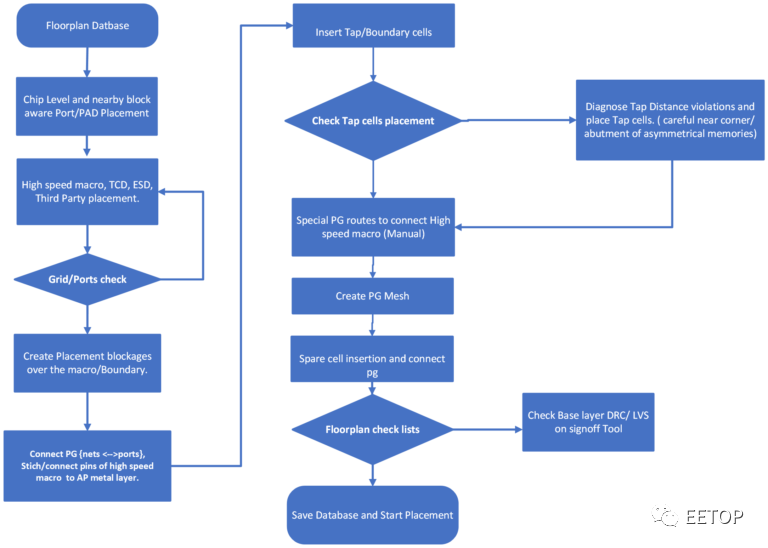

深度亚微米技术的进步,以及增加多种功能以降低成本,结合现有操作规模,意味着SoC的设计变得更加复杂。

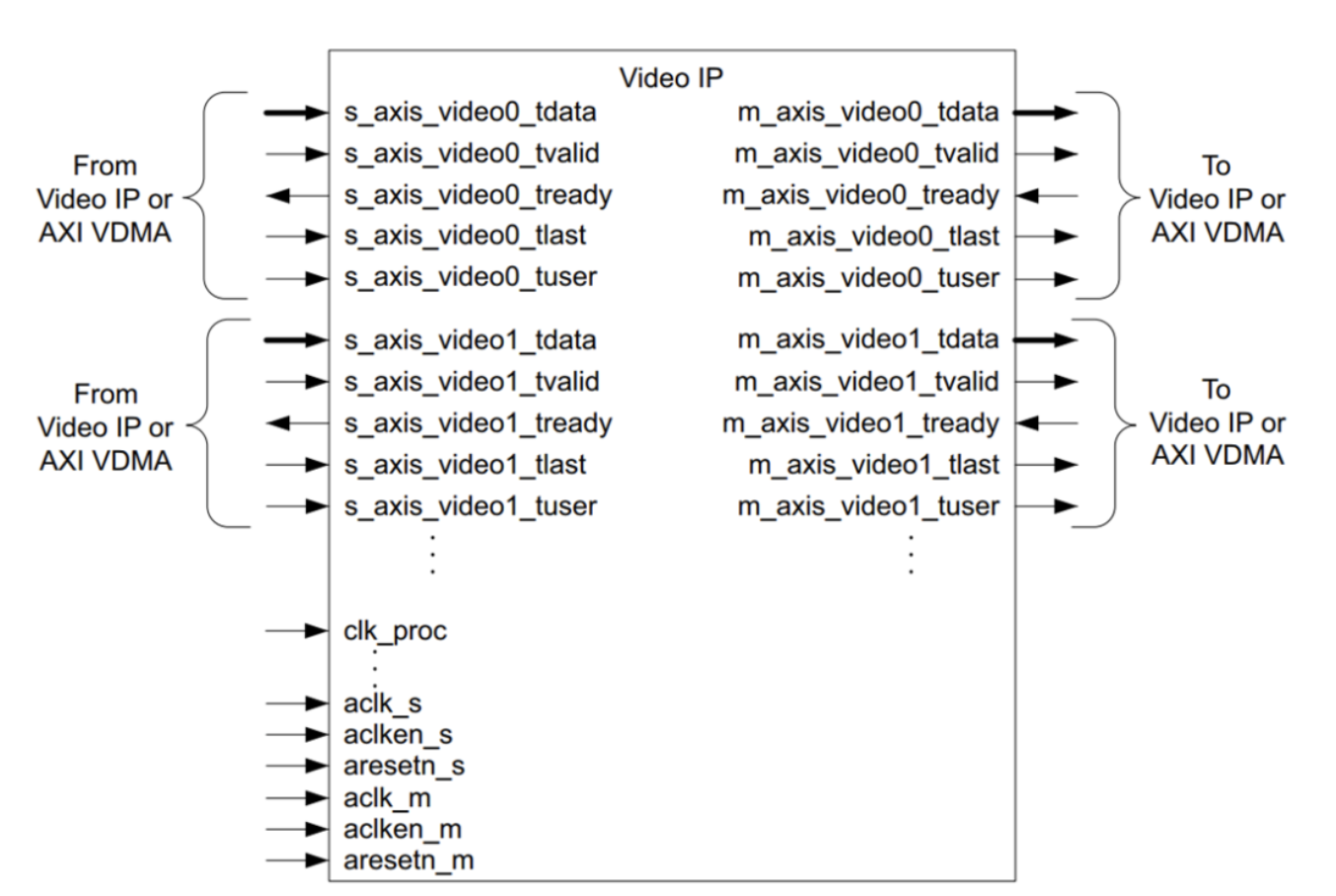

AXI4S视频IP介绍及系统设计指南(一)本文主要介绍使用AXI4S(AXI4-Stream)接口的视频IP细节。介绍本文总结了AXI4S接口视频协议,该协...

先看一组数据: 每年有超过 20 亿个终端设备搭载联发科芯片。 今年上半年全球智能手机市场份额为 38%,市占率排名第一。 而旗舰芯片天玑...

在SV中可以使用结构体作为模块的输入或输出,这使得它可以更加清晰地传递更多的信号,以简化RTL代码,类似于interface。

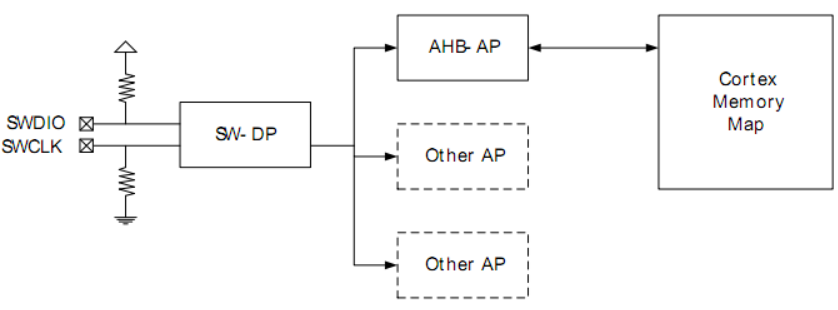

前言ARM的文档写的已经很好了,但是关于上电以后的第一时间应该怎么操作,依然写的不够清晰,导致我第一次用的时候还是费了一些周折。今...

本文是基于安谋科技“星辰”处理器的聆思科技CSK6视觉AI开发套件开发概览及介绍,资料下载以及工程师评测。

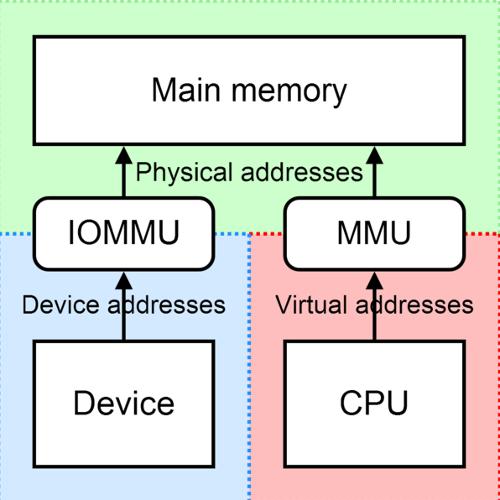

近年基于arm应用处理器的移动,infrastructure SoC平台都包含SMMUv3 IP(MMU-600,MMU-700),用于DMA mapping,VFIO,Shared Virtual Add...

这是一份针对全球多个国家,多个年龄段,使用智能手机用户的一项抽样数据调查。主要用以分析全球消费类音频设备的用户行为和需求驱动因...

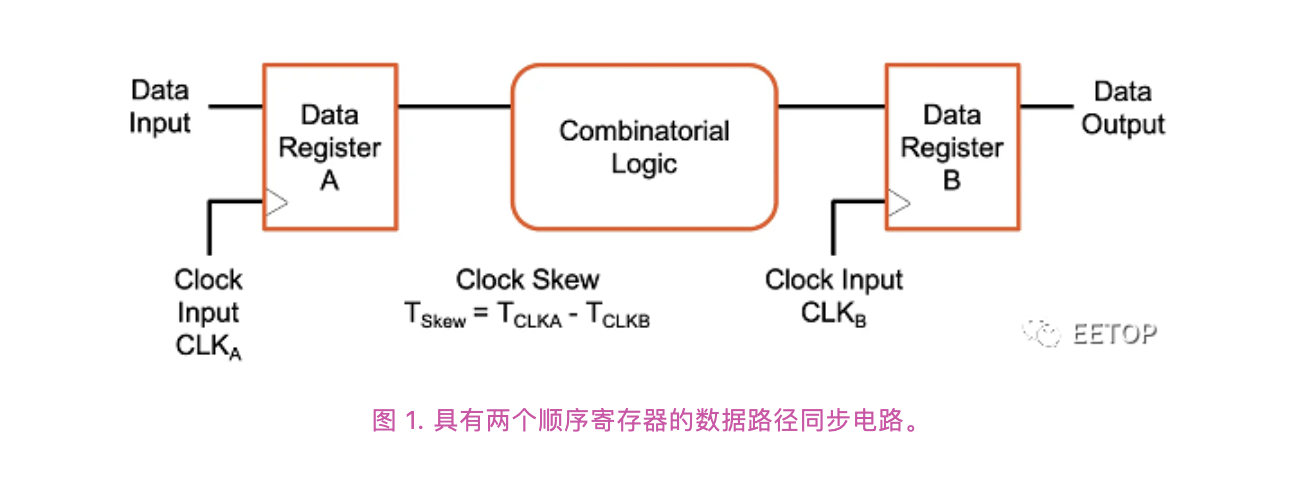

在曾经经历过在过去的好日子里,时钟信号看起来像方波,并且电压摆幅为 5V or 3.3V,但是使用 7nm 技术,时钟信号现在看起来更像锯齿信...

除了节省成本外,使用 IBIS 模型的设计人员还可以在进行电路板原型设计或制造之前预见并解决信号完整性问题,从而缩短电路板开发周期,...

本文将通过了解同步电路、时钟传输和时钟分配网络,进而了解什么是时钟偏差(clock skew)以及它对现代系统的影响。现代数字电子产品设...

CXL内存协议被称作CXL.mem。CXL.mem定义了CPU和内存之间的传输接口。该协议可用于多个不同的内存连接选项,包括当内存控制器位于主机CPU...

大家还记得那块,被RISC-V官方点赞过的开发板吗? 今天我们,再来介绍一下这块开发板 不好意思,搞错了 是介绍另一块和它长得很像的开发...

本文是读《Formal Verification An Essential Toolkit for Modern VLSI Design》第四章,做的一些笔记。

芯片巨头、创业公司纷纷下注。作者 | 范文婧编辑 | 赵健Chiplet是今年芯片领域最火的概念。海外巨头们的新产品纷纷提及Chiplet。在9月初...

本文是读《Formal Verification An Essential Toolkit for Modern VLSI Design》第三章,做的一些笔记。

众所周知,树莓派诞生之初时的设计有四大要点一个可编程的硬件(功能很强)√足够有趣,能吸引年轻人(可玩性确实高)√能反复扔进书包,...

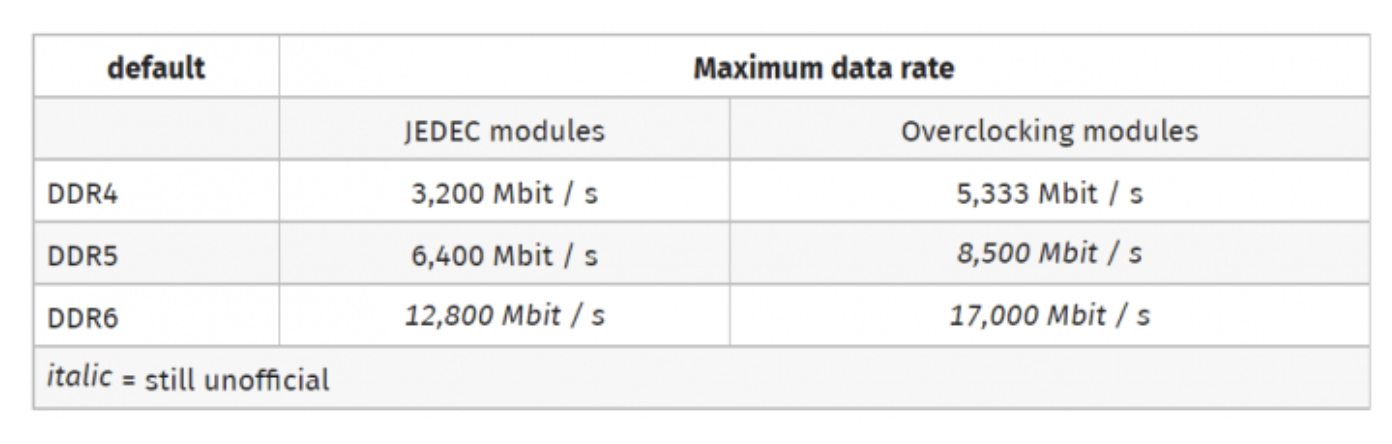

在DDR5内存刚成为主流不久,如今三星又已经率先开始了下一代DDR6内存的早期开发,并预计在2024年之前完成设计。

XGBoost(eXtreme Gradient Boosting)是一个在Gradient Boosting Decision Tree(GBDT)框架下的开源机器学习库([链接])。XGBoost用...

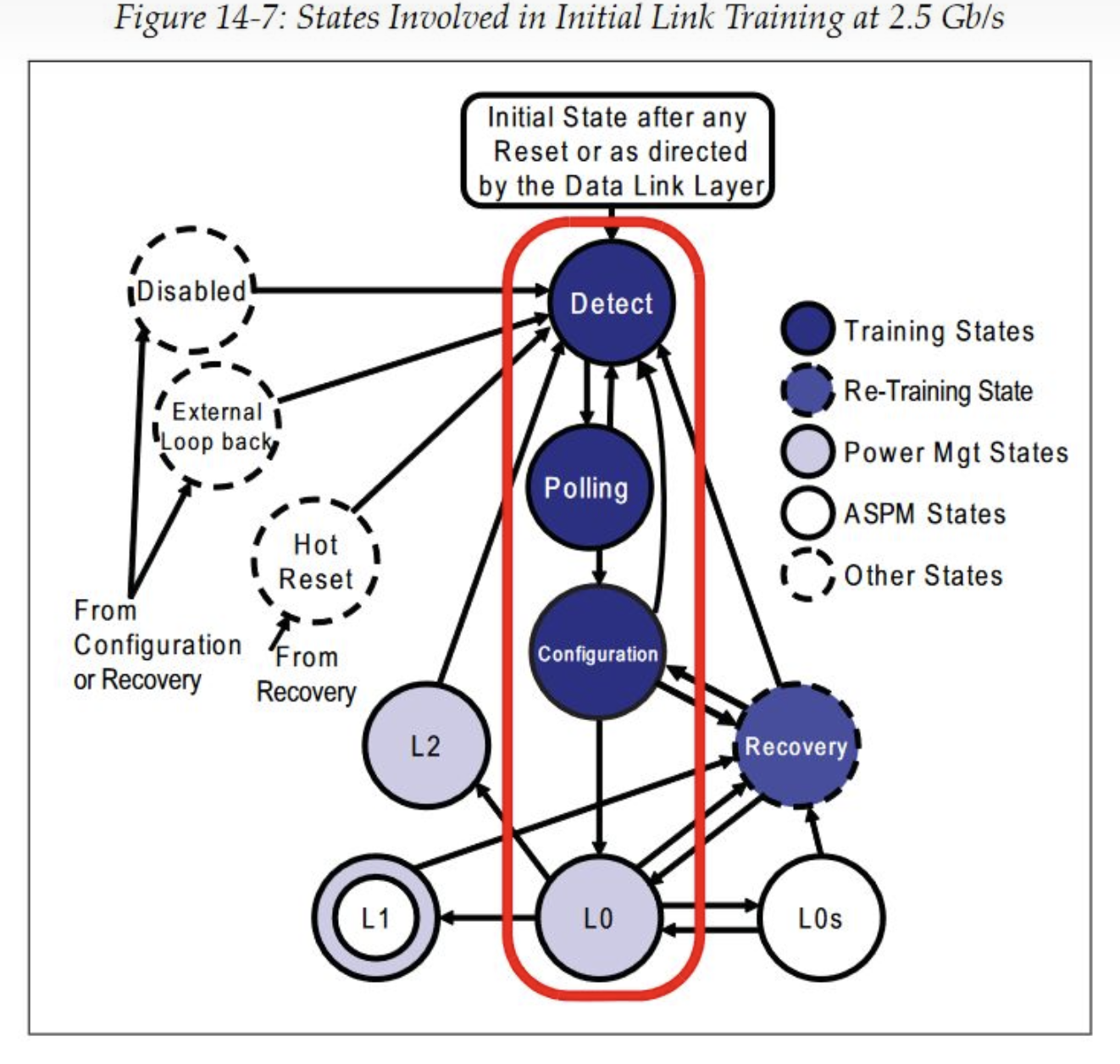

原文 519 页图 14-6 展示了 LTSSM 和链路训练的高层次抽象结构。每个 LTSSM 的状态中又划分为若干子状态。在基础复位(Fundmental Reset...

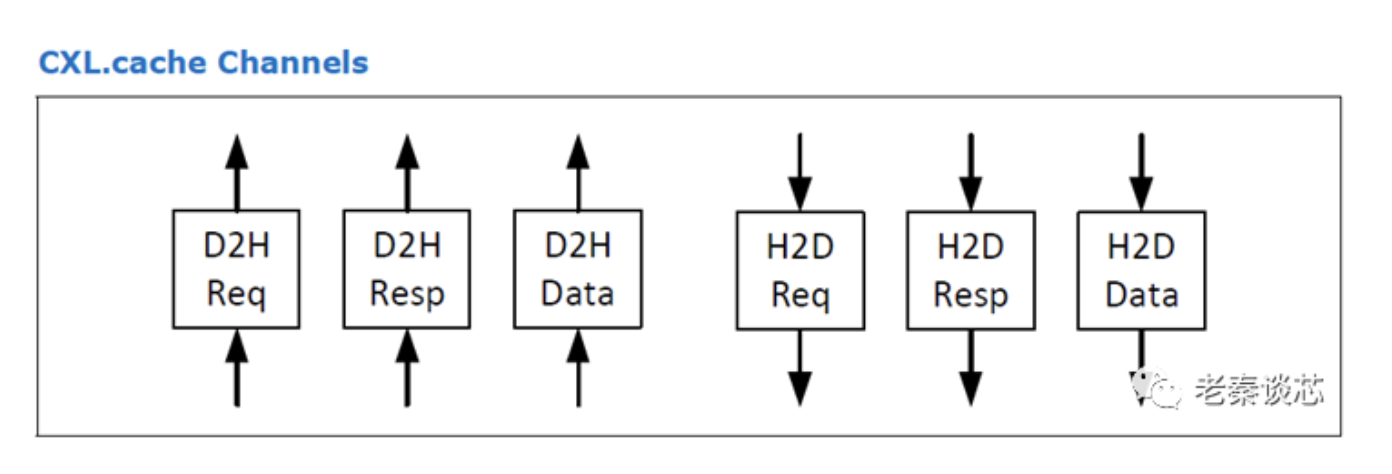

CXL.cache协议将设备和主机之间的交互定义为多个请求,每个请求至少有一条相关的响应消息,有时还有数据传输。该接口在每个方向上由三个...

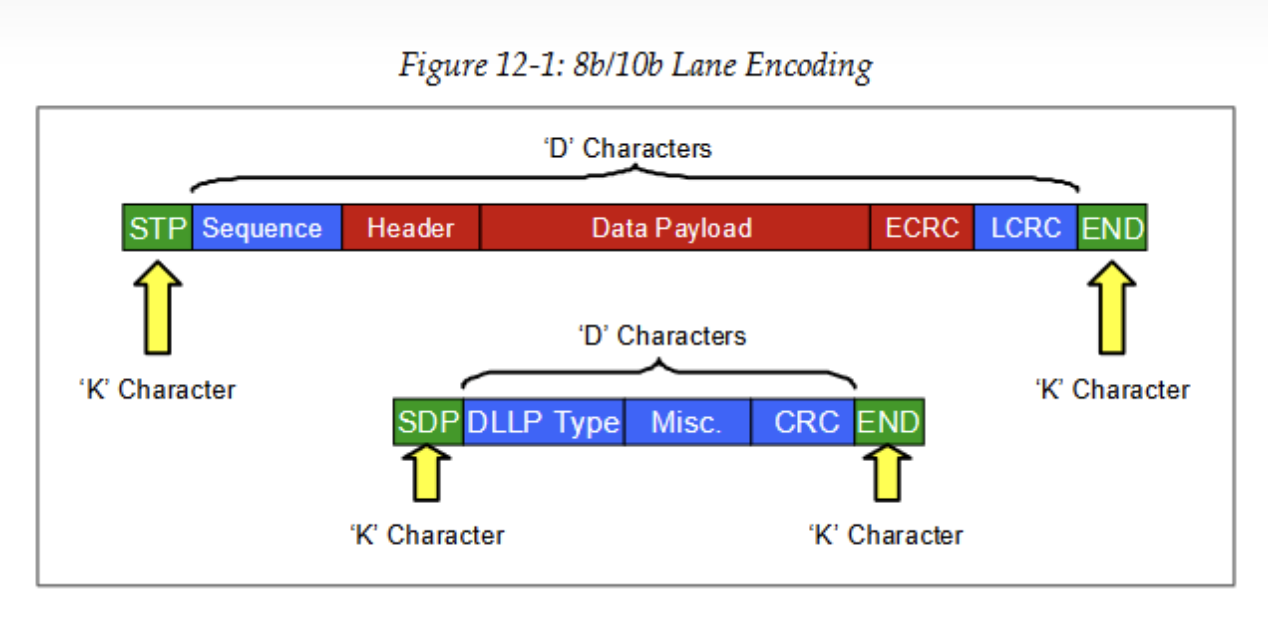

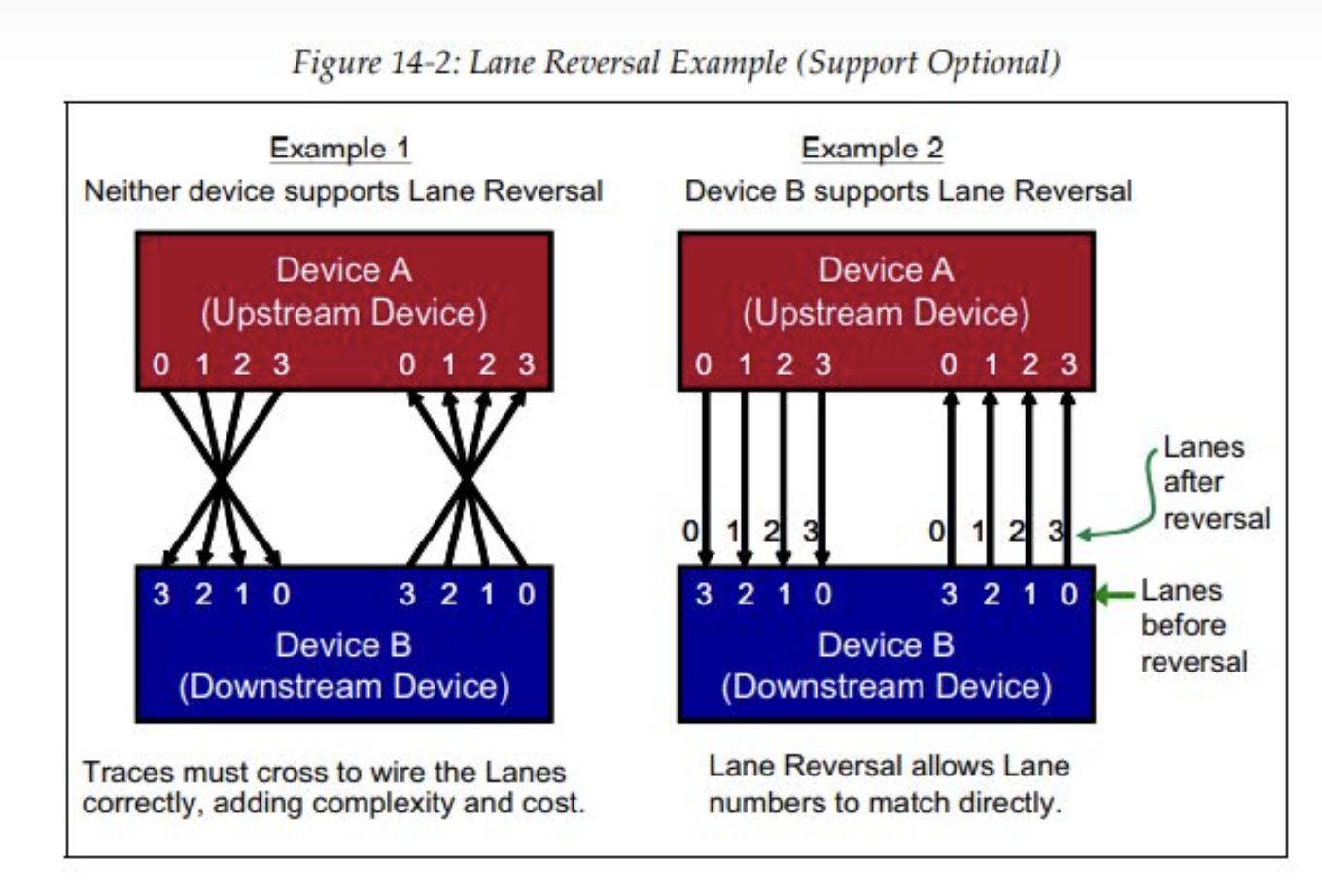

上一章描述了物理层与链路之间的电气接口,包括差分发送端与接收端的一些特性的细节。同时也讨论了信号均衡的需求以及均衡的方法。上一...

CSK6 是聆思科技新一代的 AI 芯片 SoC 产品系列,采用多核异构架构,集成了 “星辰” ARM Star MCU、HiFi4 DSP以及聆思全新设计的 AI 神经...

SDK切换存储介质需要修改board.dts、sys_config.fex、内核配置、TINA系统配置。另外,在spinor 存储介质下,通过 u-boot-sun8iw21p1.bin...

第 422 页的图 12-10 展示了支持 Gen3 速率的物理层传输逻辑的概念框图。整体设计与 Gen2 非常相似,所以没有必要再去重复讨论所有细节...